# HARMONIC REDUCTION IN CASCADED MULTILEVEL INVERTER WITH REDUCED NUMBER OF SWITCHES USING GENETIC ALGORITHMS

C. Udhaya Shankar<sup>1</sup>, J.Thamizharasi<sup>1</sup>, Rani Thottungal<sup>1</sup>, N. Nithyadevi<sup>2</sup>

<sup>1</sup>Department of EEE, Kumaraguru College of Technology, Coimbatore, India

<sup>2</sup>Department of Mathematics, Bharathiyar University, Coimbatore, India

#### **ABSTRACT**

In this paper, a new topology of cascaded multilevel inverter using a reduced number of switches is proposed. The new topology has the advantage of reduced number devices compared to traditional configurations and can be extended to any number of levels. This topology results in reduction of installation area, cost, computational time and has simplicity of control system. This structure consists of series connected sub-multilevel inverter blocks. The GA technique finds the optimal solution set of switching angles, if it exits, for each required harmonic profile. Both simulation results and experimental verification of the proposed inverter topology for different number of levels and different harmonic profiles are presented.

**KEYWORDS:** Multilevel inverter, Cascaded multilevel inverter, H –bridge, Full-bridge, Sub-multilevel inverter, Selective harmonic elimination, Programmed PWM, Genetic algorithms.

#### I. INTRODUCTION

A Multilevel inverter is a power electronic system that synthesizes a desired output voltage from several DC voltages as inputs. The concept of utilizing multiple small voltage levels to perform power conversion was presented by a MIT researcher [1,2]. Advantages of this approach include good power quality, good electro-magnetic compatibility, low switching losses and high voltage capability. The first introduced topology is the series H-bridge design [1]. This was followed by the diodeclamped inverter [2–4] which utilizes a bank of series capacitors to split the dc bus voltage. The flying-capacitor (or capacitor clamped) [5] topology uses floating capacitors to clamp the voltage levels. Another multilevel design, involves parallel connection of inverter phases through interphase reactors [6].

One particular disadvantage of multilevel inverter is the great number of power semi-conductor switches needed. So, in practical implementation, reducing the number of switches and gate driver circuits is very important.

Genetic algorithms (GAs) are stochastic optimization techniques. Genetic Algorithms are applied in this to compute the switching angles in a cascaded multilevel inverter to produce the required fundamental voltage while, at the same time, 3rd and 5<sup>th</sup> harmonics are reduced. It is shown in [7–9] that the problem of harmonic elimination is converted into an optimization task using binary coded genetic algorithms (GA). Various components of GAs such as chromosomes, fitness function, reproduction, crossover and mutation are illustrated as applied to the present work.

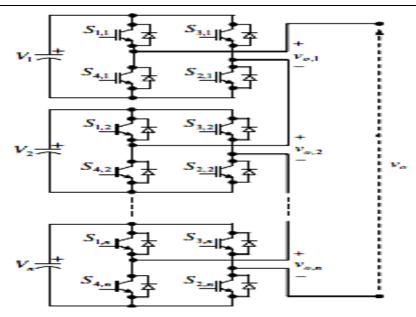

#### II. CONVENTIONAL CASCADED MULTILEVEL INVERTER

The cascaded multilevel inverter consists of series connections of n full bridge topology fig.1shows the configuration of cascaded multilevel inverter.

Fig. 1. Configuration of cascaded multilevel inverter

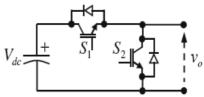

#### III. SUGGESTED TOPOLOGY

Fig. 2 shows the suggested basic unit for a sub-multilevel inverter. This consists of a capacitor (with dc voltage equal to Vdc) with two switches S1 and S2. Table 1 indicates the values of Vo for states of switches S1 and S2. It is clear that both switches S1 and S2 cannot be on simultaneously because a short circuit across the voltage Vdc would be produced. It is noted that two values can be achieved for Vo.

Fig. 2. Suggested basic unit for a sub-multilevel inverter.

**Table 1** Values of  $v_0$  for states of switches  $S_1$  and  $S_2$ .

| State | Switches states | $v_{\rm o}$    |          |

|-------|-----------------|----------------|----------|

|       | S <sub>1</sub>  | S <sub>2</sub> |          |

| 1     | On              | Off            | $V_{dc}$ |

| 2     | Off             | On             | 0        |

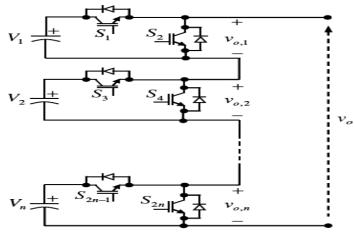

The basic unit shown in Fig. 2 can be cascaded as shown in Fig. 3.

Fig. 3. Cascaded basic unit

**Table 2** Values of  $v_0$  for state of switches.

| State          | e Switches states |       |                |       |  |            |          | $v_0$                |  |

|----------------|-------------------|-------|----------------|-------|--|------------|----------|----------------------|--|

|                | $S_1$             | $S_2$ | S <sub>3</sub> | $S_4$ |  | $S_{2n-1}$ | $S_{2n}$ |                      |  |

| 1              | Off               | On    | Off            | On    |  | Off        | On       | 0                    |  |

| 2              | On                | Off   | Off            | On    |  | Off        | On       | $v_1$                |  |

| 3              | Off               | On    | On             | Off   |  | Off        | On       | $v_2$                |  |

| 4              | On                | Off   | On             | Off   |  | Off        | On       | $V_1 + V_2$          |  |

| :              | :                 | :     | :              | :     |  | :          | :        | :                    |  |

| 2 <sup>n</sup> | On                | Off   | On             | Off   |  | On         | Off      | $\sum_{i=1}^n \nu_1$ |  |

The output voltage of conventional multilevel inverter for all times has zero or positive value. In the following, we propose a new method for determination of magnitudes of dc voltage sources which are used in the proposed multilevel inverter.

The number of maximum output voltage steps of the n series basic units can be evaluated by,

Nstep=n+1

The maximum output voltage is given by,

Vo,max=n\*Vdc

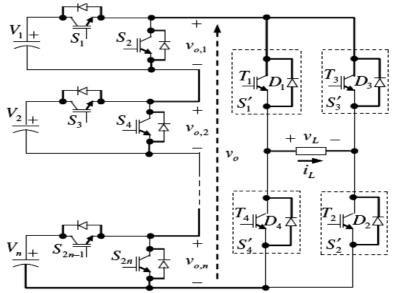

#### IV. EXTENDED STRUCTURE

Fig 4. The proposed structure for generating both positive and negative voltages

Table 3

Switches states for a full-bridge.

| State | Switch          | nes states      | ;               |                 | $v_{\mathtt{L}}$ | Components conducting                                        |  |  |

|-------|-----------------|-----------------|-----------------|-----------------|------------------|--------------------------------------------------------------|--|--|

|       | S' <sub>1</sub> | S' <sub>2</sub> | S' <sub>3</sub> | S' <sub>4</sub> |                  |                                                              |  |  |

| 1     | On              | On              | Off             | Off             | $v_{o}$          | $T_1$ and $T_2$ if $i_L > 0$<br>$D_1$ and $D_2$ if $i_L < 0$ |  |  |

| 2     | Off             | Off             | On              | On              | $-v_o$           | $D_3$ and $D_4$ if $i_L > 0$<br>$T_3$ and $T_4$ if $i_L < 0$ |  |  |

| 3     | On              | Off             | On              | Off             | 0                | $T_1$ and $D_3$ if $i_L > 0$<br>$D_1$ and $T_3$ if $i_L < 0$ |  |  |

| 4     | Off             | On              | Off             | On              | 0                | $D_4$ and $T_2$ if $I_L > 0$<br>$T_4$ and $D_2$ if $I_L < 0$ |  |  |

### V. COMPARISON OF THE SUGGESTED STRUCTURE WITH THE CONVENTIONAL MULTILEVEL INVERTER

**Table 4**Comparison of power component requirements among conventional cascaded multilevel inverters.

|                                                | Symmetrical                               | Symmetrical                                            |                                                  |

|------------------------------------------------|-------------------------------------------|--------------------------------------------------------|--------------------------------------------------|

|                                                |                                           | Binary                                                 | Trinary                                          |

| Maximum output voltage                         | $V_{dc}\left(\frac{N_{step}-1}{2}\right)$ | $V_{dc}\left(\frac{N_{step}-1}{2}\right)$              | $V_{dc}\left(\frac{N_{\text{step}}-1}{2}\right)$ |

| Number of switches, IGBTs<br>and gate drivers  | $2(N_{\text{step}}-1)$                    | $4\left[\frac{\ln(N_{\text{step}}+1)}{\ln 2}-1\right]$ | 4 ln N <sub>step</sub><br>In 3                   |

| Number of capacitors                           | $\frac{N_{\text{gep}}-1}{2}$              | $\frac{\ln(N_{\text{step}}+1)}{\ln 2}-1$               | ln N <sub>step</sub>                             |

| Variety of magnitudes of dc<br>voltage sources | 1                                         | $\frac{\ln(N_{\text{step}}+1)}{\ln 2}-1$               | ln N <sub>step</sub><br>In 3                     |

| Standing voltage                               | $2V_{\rm dc}(N_{\rm step}-1)$             | $2V_{\sf dc}(N_{\sf step}-1)$                          | $2V_{\rm dc}(N_{\rm step}-1)$                    |

Table 5

Comparison of power component requirements for suggested multilevel inverter.

| First method                              | Second<br>method                                                                                                                                                | Third method                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{dc}\left(\frac{N_{step}-1}{2}\right)$ | $V_{dc}\left(\frac{N_{step}-1}{2}\right)$                                                                                                                       | $V_{dc}\left(\frac{N_{\text{step}}-1}{2}\right)$                                                                                                                                                                                                                                                                                                                                             |

| N <sub>step</sub> + 3                     | $\frac{2\ln[2(N_{\text{step}}+1)]}{\ln 2}$                                                                                                                      | $\frac{N_{\text{step}}+9}{2}$                                                                                                                                                                                                                                                                                                                                                                |

| $\frac{N_{\text{step}}-1}{2}$             | $\frac{\ln(N_{\text{step}}+1)}{\ln 2} - 1$                                                                                                                      | N <sub>step</sub> +1                                                                                                                                                                                                                                                                                                                                                                         |

| 1                                         | $\frac{\ln(N_{\text{step}}+1)}{\ln 2}-1$                                                                                                                        | 2                                                                                                                                                                                                                                                                                                                                                                                            |

| $V_{dc}(N_{step}-1)$                      | $V_{dc}(N_{step}-1)$                                                                                                                                            | $V_{dc}(N_{step}-1)$                                                                                                                                                                                                                                                                                                                                                                         |

| $2V_{dc}(N_{step}-1)$                     | $2V_{dc}(N_{step}-1)$                                                                                                                                           | $2V_{dc}(N_{step}-1)$                                                                                                                                                                                                                                                                                                                                                                        |

| $3V_{dc}(N_{step}-1)$                     | $3V_{dc}(N_{step}-1)$                                                                                                                                           | $3V_{dc}(N_{step}-1)$                                                                                                                                                                                                                                                                                                                                                                        |

|                                           | $V_{dc}\left(\frac{N_{\text{step}}-1}{2}\right)$ $N_{\text{step}}+3$ $\frac{N_{\text{step}}-1}{2}$ $1$ $V_{dc}(N_{\text{step}}-1)$ $2V_{dc}(N_{\text{step}}-1)$ | $ \begin{array}{ccc} & & & & \\ V_{dc}\left(\frac{N_{step}-1}{2}\right) & V_{dc}\left(\frac{N_{step}-1}{2}\right) \\ N_{step}+3 & & & \frac{2\ln[2(N_{step}+1)]}{\ln 2} \\ & & & \frac{N_{step}-1}{2} & \frac{\ln(N_{step}+1)}{\ln 2}-1 \\ 1 & & & \frac{\ln(N_{step}+1)}{\ln 2}-1 \\ V_{dc}(N_{step}-1) & & V_{dc}(N_{step}-1) \\ 2V_{dc}(N_{step}-1) & & 2V_{dc}(N_{step}-1) \end{array} $ |

Tables 4 and 5 compare the power component requirements among the conventional and suggested multilevel inverters for the same number of the output voltage steps, respectively.

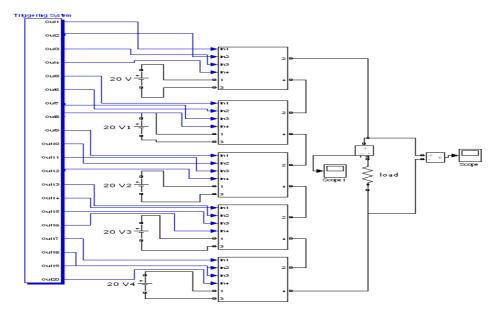

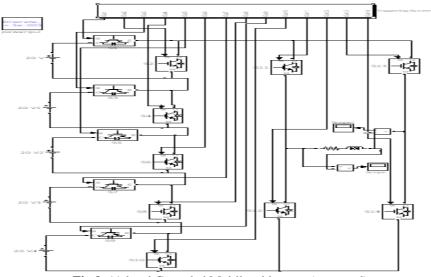

## VI. SIMULATION DIAGRAM OF 11-LEVEL (CONVENTIONAL) CASCADED MULTILEVEL INVERTER

Fig 5. 11-level Cascaded Multilevel inverter(Cascaded)

Table 5: Switching sequence for Conventional topology

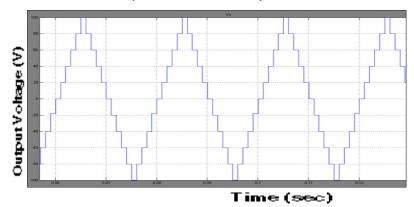

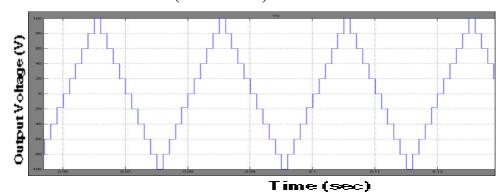

### VII. OUTPUT WAVEFORMS (CONVENTIONAL)

Fig 6.Output Voltage Waveform

Fig 7.Output Current waveform

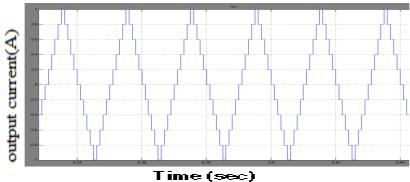

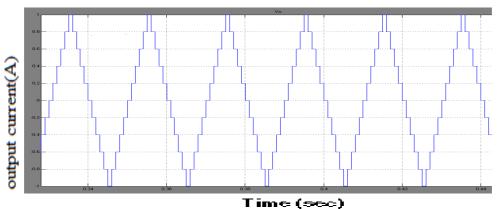

Fig 8.THD Analysis(Conventional)

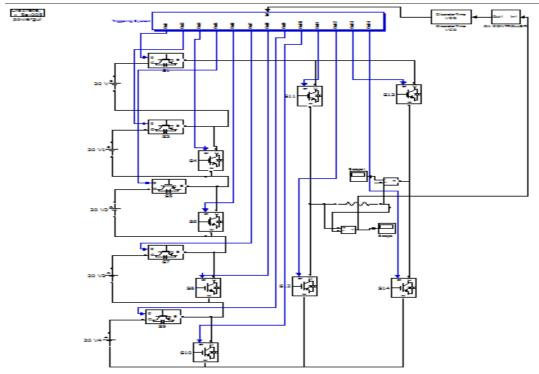

# VIII. SIMULATION DIAGRAM OF 11-LEVEL (PROPOSED) CASCADED MULTILEVEL INVERTER

Fig 9. 11-level Cascaded Multilevel inverter(proposed)

|      |    |    |    |    |    | 0  | 1  | 1  |    |     | $\mathcal{L}_{\mathcal{I}}$ |     |     |     |

|------|----|----|----|----|----|----|----|----|----|-----|-----------------------------|-----|-----|-----|

|      | S1 | S2 | S3 | S4 | S5 | S6 | S7 | S8 | S9 | S10 | S11                         | S12 | S13 | S14 |

| 0    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0                           | 0   | 0   | 0   |

| 20   | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1   | 1                           | 0   | 0   | 1   |

| 40   | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1   | 1                           | 0   | 0   | 1   |

| 60   | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 1   | 1                           | 0   | 0   | 1   |

| 80   | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1   | 1                           | 0   | 0   | 1   |

| 100  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0   | 1                           | 0   | 0   | 1   |

| 80   | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1   | 1                           | 0   | 0   | 1   |

| 60   | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 1   | 1                           | 0   | 0   | 1   |

| 40   | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1   | 1                           | 0   | 0   | 1   |

| 20   | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1   | 1                           | 0   | 0   | 1   |

| 0    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0                           | 0   | 0   | 0   |

| -20  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1   | 0                           | 1   | 1   | 0   |

| -40  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1   | 0                           | 1   | 1   | 0   |

| -60  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 1   | 0                           | 1   | 1   | 0   |

| -80  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1   | 0                           | 1   | 1   | 0   |

| -100 | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0   | 0                           | 1   | 1   | 0   |

| -80  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1   | 0                           | 1   | 1   | 0   |

| -60  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 1   | 0                           | 1   | 1   | 0   |

| -40  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1   | 0                           | 1   | 1   | 0   |

| -20  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | 1   | 0                           | 1   | 1   | 0   |

|      |    |    |    |    |    |    |    |    |    |     |                             |     |     |     |

**Table 6:** Switching sequence for proposed topology

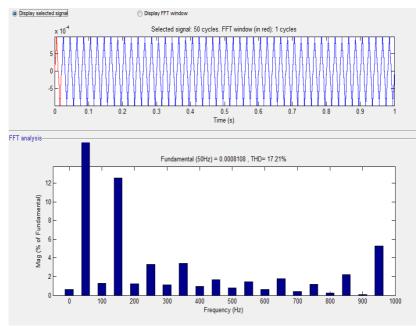

### IX. OUTPUT WAVEFORMS (PROPOSED)

Fig 10.Output Voltage Waveform

Fig 11.Output Current waveform

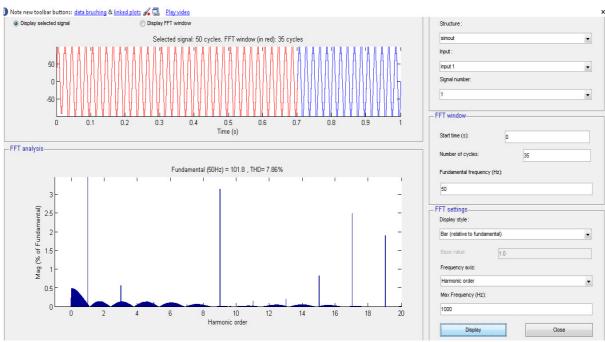

#### Fig 12.THD Analysis (Proposed)

#### X. MATHEMATICAL METHOD OF SWITCHING

The control of the new family of multilevel inverters is to choose a series of switching angles to synthesize a desired sinusoidal voltage waveform synthesized by a 2s + 1 level inverter, where s is the number of switching angles, which also equals the number of dc sources.

To reduce 3<sup>rd</sup> and 5<sup>th</sup> order harmonics in the 11-level inverter, three nonlinear equations can be set up as follows:

$$\begin{array}{l} Cos(\alpha(1)) + Cos(\alpha(2)) + Cos(\alpha(3)) + Cos(\alpha(4)) + Cos(\alpha(5)) = M \\ Cos(3\alpha(1)) + Cos(3\alpha(2)) + Cos(3\alpha(3)) + Cos(3\alpha(4)) + Cos(3\alpha(5)) = 0 \\ Cos(5\alpha(1)) + Cos(5\alpha(2)) + Cos(5\alpha(3)) + Cos(5\alpha(4)) + Cos(5\alpha(5)) = 0 \end{array}$$

Where,

Modulation index, M = Vm/5Vdc

#### XI. SOLUTION USING GENETIC ALGORITHMS

A GA for optimization is different from "classical "optimization methods in several ways: random versus deterministic operation, population versus single best solution and selecting solutions via "survival of the fittest". The solution to the harmonic elimination problem is five switching angles  $\alpha 1$ ,  $\alpha 2$ ,  $\alpha 3$ ,  $\alpha 4$ ,  $\alpha 5$ . Each switching angle is called a gene. A chromosome consists of all the genes and in this case there are five genes in one chromosome. Thus, each chromosome represents a possible solution to the problem

#### A. Encoding of a Chromosome

The population size remains constant throughout the whole process. The most used way of encoding is a binary string. Indeed, there are many other ways of encoding. The encoding depends mainly on the problem considered. In this study, a binary coding system is used. A string then could look like this (in the binary case):

String 1 1101100100110110 String 2 1101111000011110

A string in GAs may be divided into a number of substrings. The number of sub-strings, usually, equals the number of problem variables.

#### **B.** Fitness Function

The fitness function is the function responsible for evaluation of the solution at each step. The objective here is determining the switching angles such that some selected harmonics are minimized or put equal to zero.

#### C. Selection

The GA performs a selection process in which the "most fit" members of the population survive, and the "least fit" members are eliminated.

#### D. Crossover

Crossover operates on selected genes from the parent chromosomes and creates new offspring. Crossover can be illustrated as follows:(j is the crossover point):

Chromosome 1 11011j00100110110 Chromosome 2 11011j11000011110 Offspring 1 11011j11000011110 Offspring 2 11011j00100110110

#### E. Mutation

After performing crossover, mutation takes place. Mutation is used to prevent all the solutions in the population falling into a local optimum of the solved problem.. In case of binary encoding, we can switch a few randomly chosen bits from 1 to 0 or from 0 to 1.

Mutation can be illustrated as follows:

Original offspring 1 1101111000011110 Original offspring 2 1101100100110110 Mutated offspring 1 1100111000011110 Mutated offspring 2 1101101100110110

The technique of mutation (as well as crossover) depends mainly on the encoding of the chromosomes.

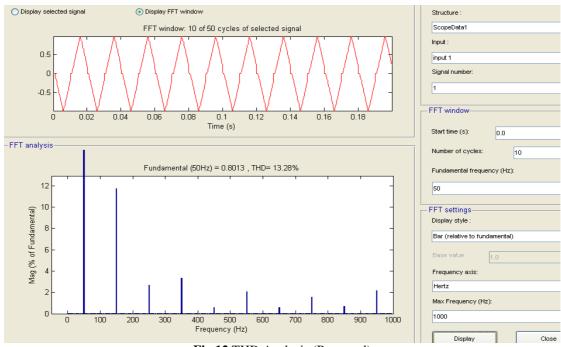

#### XII. SIMULATION DIAGRAM WITH GA CONTROLLER

Fig.13 11-level Cascaded Multilevel inverter with GA Controller

Fig 14.THD Analysis (with GA)

#### XIII. RESULTS OBTAINED

Table 7: THD Comparison

| ТҮРЕ             | THD    | 3 <sup>rd</sup> HARMONIC | 5 <sup>th</sup> HARMONIC |

|------------------|--------|--------------------------|--------------------------|

| CONVENTIONAL     | 18.75% | 13.57%                   | 4.9%                     |

| PROPOSED         | 13.27% | 11.8%                    | 2.8%                     |

| PROPOSED WITH GA | 7.86%  | 0.6%                     | Eliminated               |

In Conventional Cascaded multilevel inverter, the observed THD is **17.2** %.In our proposed topology of multilevel inverter with reduced number of switches ,the observed THD value is **13.2**% and then with GA control techniques, the THD is further reduced to 7.86% and the **3<sup>rd</sup> and 5<sup>th</sup> Order harmonics** has been eliminated.

#### XIV. CONCLUSION

The selective harmonic elimination of a new family of multilevel inverters using GA has been presented. The new configuration has the advantage of a reduced number of switching devices compared to traditional configurations of the same number of levels. The GA technique usually produces more than one possible solution set for each harmonic profile and a given specific modulation index. For multiple solutions, the solution that gives the lowest THD is selected. Both simulation and experimental results show that the algorithm can be effectively used for selective harmonic elimination of the new family of multilevel inverters and results in a dramatic decrease in the output voltage THD.

#### REFERENCES

- [1] Baker RH. Electric power converter. US Patent 03-867-643; February 1975.

- [2] Baker RH. High-voltage converter circuit. US Patent 04-203-151; May 1980.

- [3] Nabae A, Takahashi I, Akagi H. A new neutral-point clamped PWM inverter. In: Proceeding of the industry application society conference; 1980.

- [4] Fracchia M, Ghiara T, Marchesini M, Mazzucchelli M. Optimized modulation techniques for the generalized N-level converter. In: Proceeding of the IEEE power electronics specialist conference, vol. 2; 1992. p. 1205–13.

- [5] Meynard TA, Foch H. Multi-level conversion: high voltage choppers and voltage source inverters. In: Proceedings of the IEEE power electronics specialist conference, vol. 1; 1992. p. 397–403.

- [6] Ogasawara S, Takagali J, Akagi H, Nabae A. A novel control scheme of a parallel current-controlled PWM inverter. IEEE Trans Ind Appl 1992;28(5):1023–30.

- [7] B. Ozpineci, L.M. Tolbert, J.N. Chaisson, Harmonic optimization of multilevel converters using genetic algorithms, IEEE Power Electronics Lett. (2005) 1–4.

- [8] B. Ozpineci, L.M. Tolbert, J.N. Chaisson, Harmonic optimization of multilevel converters using genetic algorithms, in: Proceeding of IEEE Power Electronics Specialist Conference Letters, 2004, pp. 3911–3916.

- [9] K. Sundareswaran, A.P.Kumar, Voltage harmonic elimination in PWMA.C. chopper using genetic algorithm, IEE Pro-Electr. Power Appl. 151 (1) (2004) 26–31.

#### **Authors Biography**

**C. UDHAYA SHANKAR MIEEE**. received his B.E. degree in Electrical and Electronics Engineering from Bharathiyar University, Coimbatore India in 2001 and ME degree in Power electronics and drives from Vellore Institute of Technology, India in 2002. Recently he is a PhD candidate at Anna university of Technology, Coimbatore, India. He is currently working as Senior grade Assistant professor in Kumaraguru college of Technology, Coimbatore, India. His main interest research is optimization techniques and its application to Power Electronics, Power quality, FACTS devices and their control.

**J.THAMIZHARASI** was born in salem India, in 1989. She received the B.E (Electronics and Instrumentation Engineering) degree in Vivekanandha College of Engineering for women, Thiruchengode, India in 2010. Now she is doing M.E (Power Electronics and Drives) in Kumaraguru College of Technology, Coimbatore, India. Her areas of interest are Power Electronics and Drives, Power Quality, and Renewable Energy.

**N. NITHYADEVI** received her U.G degree in Mathematics, Kongunadu Arts and Science College, Coimbatore, India in 2000 and M.Sc degree in Mathematics from Kongunadu Arts and Science College, Coimbatore in 2002 and M.Phil from Kongunadu Arts and Science College, Coimbatore in 2003. She received her PhD for Applied Mathematics from Bharathiyar University in 2006 and she got the Post Doctoral Fellowship from National Cheng Kung University Taiwan, ROC in 2008. She is having Research and Teaching Experience of Five Years. She has presented many papers in different International Journals. She is currently working as Assistant professor in Bharathiyar University, Coimbatore, India.