# POWER ESTIMATION ANALYSIS FOR CMOS CELL STRUCTURES

Kanika Kaur<sup>1</sup> and Arti Noor<sup>2</sup>

<sup>1</sup>Department of Electronics & Comm., KIIT College of Engineering, Gurgaon, India

<sup>2</sup>M.Tech Division, CDAC, Noida, India

# **ABSTRACT**

Increasing demand for portable electronics for computing and communication, as well as other applications, has necessitated longer battery life, lower weight, and lower power consumption. In order to satisfy these requirements, research activities focusing on low power/low voltage design techniques are underway. Since 'power' is now one of the design decision variables, the expanded design space required for low power has further increased the complexity of an already non-trivial task. Low power design basically involves two concomitant tasks: power estimation and analysis and power minimization. These tasks need to be carried out at each of the levels in the design hierarchy, namely, the behavioral, architectural, logic, circuit and physical levels. In this survey of the current state of the field, many of the salient power estimation and minimization techniques proposed for low power VLSI design are reviewed. In this paper comparison of power estimation of various basic CMOS cell structures on various technologies (TSMC 0.35um, TSMC 0.2um and TSMC 0.18um) is carried out. The research issues in order to make the low power design are also discussed in the paper. The paper is organized as follows: First, the sources of power dissipation in CMOS circuits and degrees of freedom in the low power design space are described in section-2. In section-3 various power minimization techniques are discussed. Designing of various CMOS cells and Simulation results are shown in section-4&5. Athe end of the paper conclusion is given. We have used IC Design studio, HEP2 module from Mentor Graphics to obtain the simulation for various analysis of power estimation.

**KEYWORDS:** TSMC 0.12U, POWER ESTIMATION, CMOS

# I. Introduction

In the past, the major concerns of the VLSI designer were area, performance, cost and reliability; power considerations were mostly of only secondary importance. In recent years, however, this has begun to change and, increasingly, power is being given comparable weight to area and speed. Several factors have contributed to this trend. Portable computing and communication devices demand high-speed computation and complex functionality with low power consumption. Heat generation in high-end Computer products limit the feasible packing and performance of VLSI circuits and increases the packaging and cooling costs. Circuit and device reliability deteriorate with increased heat dissipation, and thus the die temperature. Heat pumped into the rooms, the electricity consumed and the office noise diminishes with low power LSI chipset. The goal of this paper is to provide background of low power design methodologies and then compare the power estimation of CMOS cell using scaling and reducing the VDD at various technology level.

# II. SOURCES OF POWER DISSIPATION

CMOS is, by far, the most common technology used for manufacturing digital ICs. There are 3 major sources of power dissipation in a CMOS circuit [9]:

$$P = P_{Switching} + P_{Short-Circuit} + P_{Leakage}$$

$P_{Switching}$ , called switching power, is due to charging and discharging capacitors driven by the circuit.  $P_{Short\text{-}Circuit}$ , called short-circuit power, is caused by the short circuit currents that arise when pairs of PMOS/NMOS transistors are conducting simultaneously.  $P_{Leakage}$ , called leakage power, originates from substrate injection and subthreshold effects. For older technologies (0.8  $\mu m$  and above), PSwitching was predominant. For deep-submicron processes,  $P_{Leakage}$  becomes more important. Design for low-power implies the ability to reduce all three components of power consumption in CMOS circuits during the development of a low power electronic product. The trend of process scaling for CMOS technology has made subthreshold leakage reduction a growing concern for submicron circuit designers.

# III. Low Power Circuit Techniques

# 3.1 Scaling the Supply Voltage

VLSI technology scaling has evolved at an amazingly fast pace for the last thirty years. Minimum device size has kept shrinking by a factor k=0.7 per technology generation. The most widely known power-reduction technique, known as power-driven voltage scaling, depending on the relative weight of performance with respect to power consumption constraints, different voltage levels can be adopted. It is important to observe, however, that transistor speed does not depend on supply voltage VDD alone, but on the gate overdrive, namely the difference between voltage supply and device threshold voltage (VDD - VT). Accurate modeling of MOS transistor currents is paramount for achieving acceptable scaled VDD and VT values.

An electronic device's overall power consumption can be represented by:

$$P_{\text{TOT}} = \alpha C_{\text{TOT}} V_{\text{DD}}^2 f + V_{\text{DD}} I_{\text{OFF}}; \text{ where } I_{\text{OFF}} = I_0 e^{(-qVTH/nkT)}$$

(1)

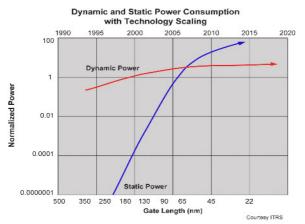

The first term in Equation 1 represents dynamic or "switching" power, while the second term represents static power—primarily due to leakage currents. (The short-circuit power, which forms less than 5% of the total power, is not included.) As a result of scaling over the years, the dynamic power has remained almost constant (see Figure 1), so increases in switching frequency ( $\alpha$ ), clock frequency (f) and total capacitance (CTOT) have been largely offset by the supply voltage (VDD). A reduction in supply voltage helps to reduce power but, on the flipside, it limits the clock frequency. Additionally, a reduction in supply voltage reduces the saturation current through the MOSFET, thereby cutting speed and performance. Hence, the supply voltage plays an important role in the speed vs. power tradeoff. To counter this reduction in saturation current, threshold voltage ( $V_{TH}$ ) has also scaled down. This has led to a tremendous surge in sub-threshold leakage current ( $I_{OFF}$ ) and static power; especially in the deep submicron process technologies (see Figure 1). Minimizing this is expected to be a significant challenge for future low-power designs. Table 1 shows the effect of scaling on various parameters

Figure 1[7]: Scaling effect on dynamic power

Table 1[7]: Effects of scaling on various parameters

| Parameter              | Relation                              | Full Scaling     | General Scaling   |

|------------------------|---------------------------------------|------------------|-------------------|

| W, L, tox              | -                                     | 1/S              | 1/S               |

| VDD, VTH               | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | 1/S              | 1/U               |

| Area                   | WL                                    | 1/S <sup>2</sup> | 1/S <sup>2</sup>  |

| Cox                    | 1/tox                                 | S                | S                 |

| CL                     | CoxWL                                 | 1/S              | 1/S               |

| IDSAT                  | Cox(W/L)V2                            | 1/S              | S/U²              |

| Intrinsic Delay (tr)   | CLV/IDSAT                             | 1/S              | U/S <sup>2</sup>  |

| Avg. Power (Pav)       | CLV <sup>2</sup> /tp                  | 1/S <sup>2</sup> | S/U <sup>3</sup>  |

| Power-Delay<br>Product | CrA5                                  | 1/S³             | 1/SU <sup>2</sup> |

Full Scaling = Dimension and voltage scales by a factor "S" (S>0)

General Scaling = Dimension and voltage scales with different factors

©IJAET ISSN: 2231-1963

#### 3.2 Power Distribution

As the supply voltage is reduced, the noise margins are diminished, thus, small voltage drop in the power distribution may have a relatively big impact on the circuit speed. Careful power distribution is thus becoming more important at lower supply voltages. In [57], a technique for concurrent topology design and wire sizing in power distribution networks is presented. The objective is to minimize the layout area while limiting the average current density to avoid electro migration- induced reliability problems and large resistive voltage drops. This technique is based on the observation that when two sinks do not draw currents at the same time, narrow wires can be used for power distribution to those sinks, thus reducing the layout area.

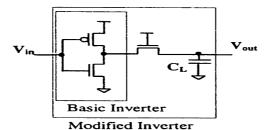

### 3.3 Reduce Output Voltage Swing

For a further power reduction the output voltage swing can be reduce to a value less than a supply voltage. Since the delay is proportional to the signal swing (Vswing), reducing the signal swing linearly decreases the delay, as well as, for constant  $I_{avg}$  [32]. To limit the swing of any static or dynamic CMOS circuit that has a rail to rail swing, extra circuitry is required as shown in fig. 2 [33]. This extra circuitry adds parasitic capacitance that add to the total effective capacitance being switched. However, the total energy is reduced because the voltage swing has been reduced. As long as the reduction in voltage swing is greater than the increase in capacitance, the energy and power will be reduced [33].

Fig.2 [33]: A reduced swing CMOS inverter

#### 3.4 Reducing the physical Capacitance

Digital circuits have three types of capacitance: gate capacitance, diffusion capacitance and interconnect capacitance. If all the three components are scaled down as well by the same factor, then the net power dissipation is scaled down as well. Gate and diffusion capacitance are fixed during the cell design, whereas Intercell and global interconnect capacitances can be controlled by the CAD tools performing the global routing. Physical capacitance mainly reduces by the transistor sizing[42].

### 3.5 Reducing the switching frequency

Reducing the number of "0" to '1" power dissipating transitions minimize the switching power dissipation of the gate .Switching frequency may be reduced on several levels in the design process beginning from circuit level to the architectural level [23]. There are several logic styles to design with. Some of these styles are: Static CMOS, CPL, MCML, and a variety of dynamic logic styles. Generally, most logic styles perform delay power tradeoffs, but not always in proportional amounts. The best style is that which minimize power dissipation given a constant throughput.

# IV. DESIGNING AND POWER ANALYSIS OF DIFFERENT CMOS CELLS

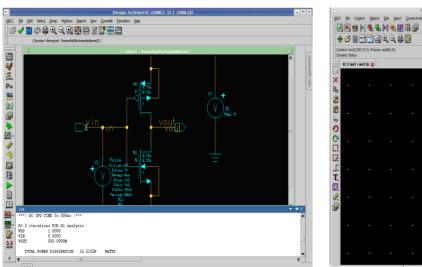

This section describes the design of various CMOS cell using technology scaling and reducing the supply voltage using TSMC 0.35u, TSMC 0.2u and TSMC 0.18u for simulation. First the basic CMOS inverter with a values of W/L for PMOS =  $(1.2\mu m/0.18 \ \mu m)$  and W/L for NMOS =  $(0.27 \ \mu m/0.18 \ \mu m)$  is analyzed using MENTOR GRAPHICS, IC DESIGN STUDIO, HEP2 software in detail and then, based on this analysis, the NAND and the NOR gates are designed and after that other circuits can also be designed by calculating the values of W/L at scaled Vdd.

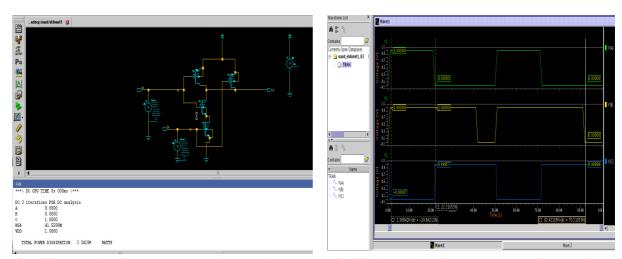

# 4.1 Result for TSMC 0.18u technology with Vdd= 2v, shows power dissipation 129.54p watts for CMOS Inverter

Fig. 3.1 Schematic of Inverter of 0.18u, 2V

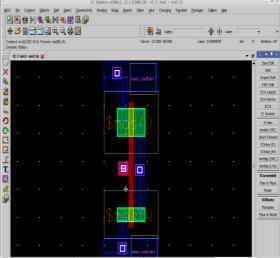

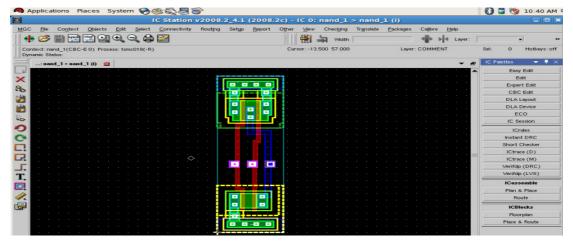

Fig.3.2 Layout of Inverter

4.2 Results for TSMC 0.18u technology with Vdd= 1v, shows power dissipation 16.5125p watts for CMOS Inverter

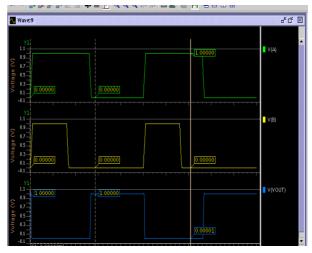

Fig. 4.2 Simulation of Inverter of 0.18 u of 1V

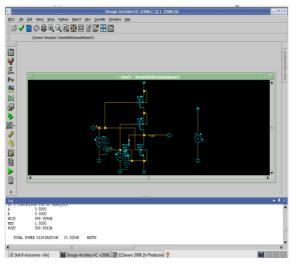

4.3 Results for 0.25u technology with Vdd= 1v, shows power dissipation 20.8509p watts for CMOS Inverter

Fig. 5 Schematic of Inverter of 0.25u of 1V

# 4.4 Results for 0.35u technology with Vdd= 1v, shows power dissipation 38.1579p watts for CMOS Inverter

Fig. 6 Schematic of Inverter of 0.35u of 1V

# V. DESIGN, LAYOUT AND SIMULATION OF DIFFERENT CMOS CIRCUITS

# 5.1 Two input CMOS NAND Gate

Results for 0.18u technology with Vdd= 1V, shows power dissipation 2.963p watts for CMOS NAND gate

Fig. 6.1 Schematic of CMOS NAND of 0.18u of 1V

Fig. 6.2 Simulation of CMOS NAND of 0.18u of 1V

Fig. 6.3 Layout of CMOS NAND of 0.18u of 1V

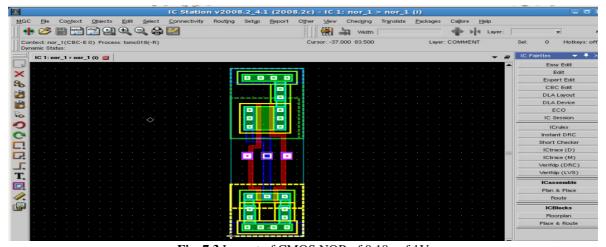

#### 5.2 Two input CMOS NOR Gate

Results for 0.18u technology with Vdd= 1V, shows power dissipation 33.12p watts for CMOS NOR gate

Fig. 7.1 Schematic of CMOS NOR of 0.18u of 1V

Fig. 7.2 Simulation of CMOS NOR of 0.18u of 1V

Fig. 7.3 Layout of CMOS NOR of 0.18u of 1V

Table 2: Power dissipation in Different CMOS Cell

| CMOS Cell     | Power Dissipation at various technology at 1V Vdd(watts) |           |            |  |

|---------------|----------------------------------------------------------|-----------|------------|--|

|               | TSMC 0.35u                                               | TSMC 0.2u | TSMC 0.18u |  |

| CMOS          | 38.1579p                                                 | 20.8509p  | 16.5125p   |  |

| INVERTER      |                                                          |           |            |  |

| CMOS NAND     | 14.959p                                                  | 3.9799p   | 2.963p     |  |

| Gate          |                                                          |           |            |  |

| CMOS NOR Gate | 45.035p                                                  | 36.032p   | 33.250p    |  |

# VI. CONCLUSION

Based on scaling various analysis of power estimation have been done and conclude that by reducing the power supply and technology scaling significant power reduction is take place. Return-On-Investment approach is through designing for low power. Unfortunately designing for low power adds another dimension to the already complex design problem; the design has to be optimized for Power as well as Performance and Area. Future Challenges ahead us are:-

- High-speed & Low power design is a requirement for many applications

- A new way of THINKING to simultaneously achieve both!!!

- Low power impacts in the cost, size, weight, performance, and reliability.

- Variable Vdd and Vt is a trend

- CAD tools high level power estimation and management

#### **REFERENCES**

- [1] S. Hanson, B. Zhai, K. Bernstein, D. Blaauw, A. Bryant, L. Chang, K. K. Das, W. Haensch, E. J. Nowak and D. Sylvester,

- "Ultralow-voltage, minimum-energy CMOS," IBM Journal of Research and Development, vol. 50, no. 4-5, pp. 469–490, 2006.

- [2] A. P. Chandrakasan, S. Sheng and R. W. Brodersen, "Low Power CMOS Digital Design," IEEE Journal of Solid-state Circuits,

- vol. 27, no. 4, pp. 473-484, April 1999.

- [3] K. Ragini and B. K. Madhavi, "Ultra Low Power Digital Logic Circuits in Subthreshold for Biomedical Applications," Journal

- of Theoretical and Applied Information Technology, 2005.

- [4] K. Roy, S. Mukhopadhyay, and H. Mahmoodi-Meimand, "Leakage current mechanisms and leakage reduction techniques

- in deep-submicrometer cmos circuits," in Proceedings of IEEE, vol. 91, no. 2, pp. 305-327, 2003.

- [5] R. Corless, G. Gonnet, D. Hare, D. Jeffrey and D. Knuth, "On the Lambert W function," Advance in Computational Mathematics,

- vol. 5, pp. 329-359, 1996.

- [6] A. Wang, B. H. Calhoun and A. P. Chandrakasan, Subthreshold Design For Ultra Low-Power Systems, Springer, USA, 2006.

- [7] R. M. Swanson and J. D. Meindl, "Ion-Implanted Complementary MOS Transistors in Low-Voltage Circuits," IEEE Journal of

- Solid-State Circuits, vol. 7, no. 2, pp. 146-153, April. 1972.

- [8] S. M. Kang and Y Leblebici, CMOS Digital Integrated Circuits: Analysis and Design, 3rd ed, McGraw Hill, 2004.

- [9] H. Bakoglu, Circuits, Interconnections, and Packaging for VLSI. Addison-Wesley, Menlo Park, CA, 1990.

- [10] M. Berkelaar and J. Jess. " Gate sizing in MOS digital circuits with linear programming. " In Proceedings of the European Design Automation Conference, pages 217-221, 1990.

- [11] M. Borah, R. M. Owens and M. J. Irwin. "Transistor sizing for minimizing power consumption of CMOS circuits under delay constraint. "In Proceedings of the 1995 International Symposium on Low Power Design, pages 167-172, April 1995.

- [12] M. Burstein and R. Pelavin. "Hierarchical channel router." In Proceedings of the 20<sup>th</sup> Design Automation Conference, pages 591-597, 1983.

- [13] K. Y. Chao and D. F. Wong. "Low-power consideration in floorplan design. "In Proceedings of the 1994 International Workshop on Low Power Design, pages 45-50, April 1994.

- [14]J. Cong, C-K. Koh and K-S. Leung. "Simultaneous driver and wire sizing for performance and power optimization." IEEE Transactions on VLSI Systems, 2(4):408-425, December 1994.

- [15] J. Cong and K-S. Leung. "Optimal wire sizing under Elmore delay model. "IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 14(3):321-336, March1995.

- [16] J. Cong and C-K. Koh. " Minimum-cost bounded-skew clock routing. " In Proceedings of the International Symposium on Circuits and Systems, pages 215-218, 1995.

- [18] D. N. Deutch. " A dogleg channel router. " In Proceedings of the 13th Design Automation Conference, pages 425-433, 1976.

- [19] D. Dobberpuhl et al, " A 200MHz, 64b, dual issue CMOS microprocessor. " Digest of Technical Papers, ISSC '92, pages 106-107, 1992.

- [20] M. Edahiro. " A clustering-based optimization algorithm in zero-skew routings. " In Proceedings of the 30th Design Automation Conference, pages 612-616, June 1993.

- [21] M. Edahiro. "Delay minimization for zero-skew routing." In Proceedings of the International Conference on Computer Design, pages 563-566, November 1993.

- [22] B. J. George, D. Gossain, S. C. Tyler, M. G. Wloka, and G. K. H. Yeap. "Power analysis and characterization for semi-custom design." In Proceedings of the 1994 International Workshop on Low Power Design, pages 215–218, April 1994.

- [23] X. L. Hong, J. Huang, C. K. Cheng, and E. S. Kuh. "FARM: an efficient feed-through pin assignment algorithm." In Proceedings of the 29th Design Automation Conference, pages 530-535, June 1992.

- [24] A. Hashimoto and J. Stevens. "Wire routing by optimization channel assignment within large apertures." In Proceedings of the 8th Design Automation Workshop, pages 155-163, 1971.

- [25] N. Hedenstierna and K. Jeppson. "CMOS circuit speed and buffer optimization." IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 6(3):270-281, March 1987.

- [26] D. J. Huang, A. B. Kahng and C. W. Tsao. "On the bounded-skew clock and Steiner tree problems." In Proceedings of the 32nd Design Automation Conference, pages 508-513, June 1995.

- [27] S. M. Kang and Y. Leblebici. CMOS Digital Integrated Circuits: Analysis and Design. McGraw-Hill Companies, Inc. 1996.

- [28] B. W. Kernighan and S. Lin. " An efficient heuristic procedure for partitioning graphs. " Bell System Technical Journal, 49(2):291-307, February 1970.

- [29] S. Kirkpatrick and C. D. Gelatt and M. P.Vecchi. "Optimization by simulated annealing. "Science, 220(4598):671-680, May 1983.

- [30] J. M. Kleinhans, G. Sigl, F. M. Johannes and K. J. Antreich. "GORDIAN: VLSI placement by quadratic programming and slicing optimization." IEEE Transactions onComputer-Aided Design of Integrated Circuits and Systems, 10(3):356-365, March 1991.

- [31] E. L. Lawler and K. N. Levitt and J. Turner. "Module clustering to minimize delay in digital networks." IEEE *Transactions on Computers*, pages 45-57, January 1969.

- [32] K. W. Lee and C. Sechen. " A new global router for row-based layout. " In *Proceedings of the I EEE International Conference on Computer Aided Design*, pages 180-183, November 1988.

- [33] J. Lillis, C-K Cheng and T-T. Y. Lin. "Optimal wire sizing and buffer insertion for low power and a generalized delay model" In *Proceedings of the International Conference on Computer Design*, pages 138-143, November 1995.

- [34] H-R. Lin and T-T. Hwang. "Power reduction by gate sizing with path-oriented slack calculation." In *Proceedings of the 1st Asia-Pacific Design Automation Conference*, pages 7-12, August 1995.

- [35] G. Meixner and U. Lauther. " A new global router based on a flow model and linear assignment. " In *Proceedings of the IEEE International Conference on Computer Aided Design*, pages 44-47, November 1990.

- [36] N. Menezes, R. Baldick and L. T. Pileggi. " A sequential quadratic programming approach to concurrent gate and wire sizing. " In *Proceedings of the IEEE International Conference on Computer Aided Design*, pages 144-151. November 1995.

- [37] J. Oh and M. Pedram. "Constructing lower and upper bounded delay routing trees using linear programming." To appear in *Proceedings of the 33rd Design Automation Conference*, June 1996.

- [38] T. Okamoto, M. Ishikawa, and T. Fujita. "A new feed-through assignment algorithm based on a flow model." In *Proceedings of the 30th Design Automation Conference*, pages 775-778, June 1993.

- [39] T. M. Parng and R. S. Tsay. " A new approach to sea-of-gates global routing. " In *Proceedings of the IEEE International Conference on Computer Aided Design*, pages 52-55, November 1989.

- [40] M. Pedram, M. Marek-Sadowska and E. S. Kuh. "Floorplanning with pin assignment." In *Proceedings of the IEEE International Conference on Computer Aided Design*, pages 98-101, November 1990.

- [41] M. Pedram. "Power estimation and optimization at the logic level. "Int'l Journal of High Speed Electronics and Systems, 5(2):179-202, June 1994.

- [42] S. C. Prasad and K. Roy. "Circuit optimization for minimization of power consumption under delay constraint. "In *Proceedings of the 1994 International Workshop on LowPower Design*, pages 15-20, April 1994.

- [43] S. Pullela, N. Menezes and L. T. Pillage. "Reliable non-zero skew clock tree using wire width minimization." In *Proceedings of the 30th Design Automation Conference*, pages 165-170, June 1993.

- [44] S. Pullela, N. Menezes, J. Omar and L. T. Pillage. "Skew and delay optimization for eliable buffered clock trees." In *Proceedings of the IEEE International Conference on Computer Aided Design*, pages 556-562, November 1993.

#### **Authors Biographies**

Kanika Kaur (Associate Professor, KIIT, Gurgaon) received B.Sc (Electronics) Hons. Degree from Delhi University in 1997 and M.Sc (Electronics) Hons. Degree from Jamia Millia Islamia University in 1999. She received M.Tech degree from RTU in 2005 and presently pursuing Ph.D from the JJTU, Rajasthan in the field of "Low power VLSI design-subthreshold leakage reduction technique for CMOS". Published more than 20 research papers in national, international journal & conferences. She has also published a book titled "Digital System Design" by SciTech Publication in 2009. Editor of 05 Technical Proceedings of National & International Seminars. Convener of many National and International Symposium. Life member of IETE & ISTE. Awarded as best

academic personality& HOD in 2007 and 2008 NIEC, Delhi. Convener of Research Journal of KIIT College of Engineering.

Arti Noor (Associate Professor) received B. Sc. And M. Sc. (Electronics) degree from Rohilkhand University Bareilly in 1983 & 1985, respectively. She received PhD degree in Microelectronics from Institute of Technology, BHU, Varanasi in 1990. She is currently Scientist-E (Associate Professor) and Head of department, in M.Tech VLSI Design, CDAC Noida. She published more than 20 research papers in national, international journals and conferences. Her research interest includes VLSI Design of semi or full custom chips for implementation of specific architecture, Low power VLSI Design, Digital Design, Mixed signal circuit design and RF cell library design using VHDL/Verilog-AMS Language.