# DEEP SUB-MICRON SRAM DESIGN FOR DRV ANALYSIS AND LOW LEAKAGE

Sanjay Kr Singh<sup>1</sup>, Sampath Kumar<sup>2</sup>, Arti Noor<sup>3</sup>, D. S. Chauhan<sup>4</sup> & B.K.Kaushik<sup>5</sup>

<sup>1</sup>IPEC, Ghaziabad, India.

<sup>2</sup>J.S.S. Academy of Technical Education, Noida, India.

<sup>3</sup>Centre for Development of Advance Computing, Noida, India.

<sup>4</sup>UTU, Dehradun, India.

<sup>5</sup>IIT Roorkee, India.

## **ABSTRACT**

*This paper deals with the design opportunities of Static Random Access Memory (SRAM) for lower power consumption and propagation delay. Initially the existing SRAM architectures are investigated, and thereafter a suitable basic 6T SRAM structure is chosen. The key to low power dissipation in the SRAM data path is to reduce the signal swings on the highly capacitive nodes like the bit and data lines. While designing the SRAM, techniques such as circuit partitioning, divide word line and low power layout methodologies are reviewed to minimize the power dissipation.*

**KEYWORDS:** SRAM, SNM, DRV, SOC, CMOS, DIBL

## **I. INTRODUCTION**

Ever since the early days of semiconductor electronics, there has been a desire to miniaturize the components, improve their reliability and reduce the weight of the system. All of these goals can be achieved by integrating more components on the same die to include increasingly complex electronic functions on a limited area with minimum weight. Another important factor of successful proliferation of integration is the reduced system cost and improved performance.

SRAM cell design considerations are important because of following reasons.

1. The design of an SRAM cell is key to ensure stable and robust SRAM operation.

2. The continuous drive to enhance the on-chip storage capacity; the SRAM designers are motivated to increase the packing density. Therefore, an SRAM cell must be as small as possible while meeting the stability, speed, power and yield constraints.

3. Near minimum size cell transistors exhibit higher susceptibility with respect to process variations.

4. The cell layout largely determines the SRAM critical area, which is the chip yield limiter.

5. In scaled technologies the cell stability is of paramount significance. Static Noise Margin (SNM) of a cell is a measure of its stability

A significantly large segment of modern SoCs is occupied by SRAMs. SRAM content in ASIC domain is also increasing. Therefore, understanding SRAM design and operation is crucial for enhancing various aspects of chip design and manufacturing. The memory leakage power [13] has been increasing dramatically and becomes one of the main challenges in future system-on-a-chip (SoC) design.

For mobile applications low standby power [4] [16] is crucial. A mobile device often operates in the standby mode. As a result, the standby leakage power has a large impact on the device battery life. Memory leakage suppression [18] is important for both high speed and low power SoC designs. A large variety of circuit design techniques available to reduce the leakage power of SRAM cells and the memory peripheral circuits.

In recent years, significant progress has been made in design and development of low power electronics circuits. Power dissipation has become a topic of intense research and development of portable electronic devices and systems. In VLSI chip, with higher levels of integration, packaging density of transistors is increasing. As a result, for high levels of integration power dissipation

becomes the dominant factor. CMOS technology is known for using low power at low frequency with high integration density. There are two main components that determine the power dissipation of a CMOS gate, first component is the static power dissipation [9] due to leakage current and second component is the dynamic power dissipation [10] due to switching transient current and charging/discharging of load capacitance. In order to accurately determine the heat produced in a chip, one must determine the power dissipated by the number of gates and the number of off-chip drivers and receivers.

The need for low power design [11] [10] is becoming a major issue in high performance digital systems, such as portable communication devices, microprocessors, DSP's and embedded throughput. Hence low power design of digital integrated circuits has emerged as a very active developing field. As integrated chip designers accelerate their adoption of today's deep sub micron semiconductor (DSM) technologies, squeezing the maximum transistor count into and the maximum performance, minimum power and noise out of their high performance designs, increasing importance is placed on the accuracy of cell characterization systems. The common traits of high-performance chips are the high integration density and high clock frequency. The power dissipation of the chip increases with the increasing clock frequency. In most of the real time applications, the requirements for low power consumption must be met along with the high chip density.

In this paper, a circuit level leakage technique is adapted for the core cell to minimize the leakage by having good data stability. In section II, the SRAM cell design opportunities are explained and corresponding design trade-offs are listed. The existing leakage techniques are investigated and optimal  $V_{DD}$  value is fixed with the help of SNM and DRV in section III. The simulation results are presented to compare the stability and optimal VDD are given in section IV and conclusion is given in section V.

## II. SRAM DESIGN OPPORTUNITIES

Modern SRAMs strive to increase bit counts while maintaining low power consumption [6] and high performance. These objectives require continuous scaling of CMOS transistors. The supply voltage must scale down accordingly to control the power consumption and maintain the device reliability. Scaling the supply voltage and minimum transistor dimensions that are used in SRAM cells challenge the process and design engineers to achieve reliable data storage in SRAM arrays. This task is particularly difficult in large SRAM arrays that can contain millions of bits. Random fluctuations in the number and location of the doping atoms in the channel induce large threshold [5] voltage fluctuations in scaled-down transistors.

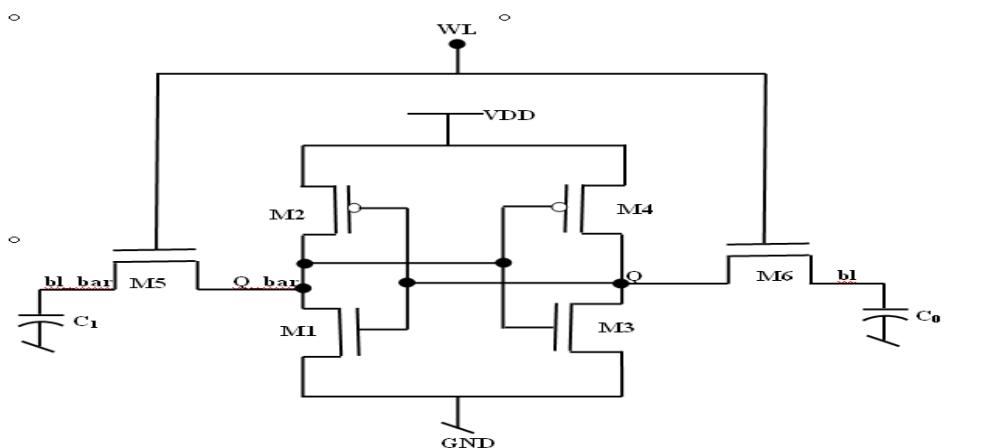

Figure 1. Schematic of SRAM cell

Other factors affecting the repeatability of the threshold voltage and introducing  $V_{TH}$  mismatches even between the neighboring transistors in SRAM cells are the line edge roughness, the variations of the poly critical dimensions and the short channel effects. SRAM stability margin or the Static Noise Margin (SNM) is projected to reduce by 4X as scaling progresses from 250 nm CMOS technology down to 50 nm technology [3]. Since the stability of SRAM cells is reducing with the technology scaling, accurate estimation of SRAM data storage stability in pre-silicon design stage and verification of SRAM stability in the post-silicon testing stage are increasingly important steps in SRAM design.

### III. EXISTING AND PROPOSED WORK

A large variety of circuit design techniques used to reduce the leakage power of SRAM cells and the memory peripheral circuits (decoding circuitry, I/O, etc). The leakage of the peripheral circuits can be effectively suppressed by turning off the leakage paths with switched source impedance (SSI) during idle period. Our work focuses on the leakage control of 6T -structure SRAM core cell of Fig 1 during the standby mode. The existing SRAM cell leakage reduction techniques include novel SRAM cell design, dynamic-biasing [1], and VDD-gating. Memory operations at such a low voltage effectively reduce both the active and standby power.

The dynamic-biasing techniques use dynamic control on transistor gate-source and substrate-source bias to enhance the driving strength of active operations and create low leakage paths during standby period. At the current technology nodes (130nm and 90nm), the above dynamic-biasing schemes typically achieve 5-7X leakage power reduction. This power saving becomes less as the technology scales, because the worsening short-channel effects cause the reverse body bias effect on leakage suppression to diminish [12]. In order to design for a higher (>30X) and sustainable leakage power reduction [7], an SRAM designer needs to integrate multiple low-power design techniques, rather than using dynamic-biasing only.

The VDD-gating techniques either gate-off the supply voltage of idle memory sections, or put less frequently used sections into a low-voltage standby mode. There are three types of leakage mechanisms in an SRAM cell: sub-threshold leakage, gate leakage and junction leakage. A lower VDD reduces all of these leakages effectively. The reduction ratio in leakage power is even higher because both the supply voltage and leakage current are reduced. In recent years as the need of leakage reduction in high-utilization memory structures increases, there have been many research activities on low-voltage SRAM standby techniques.

Although the available techniques can be very effective in enhancing the efficiency of low-voltage memory standby operation, an important parameter needed by all of these schemes is the value of SRAM standby VDD. This is because a high standby VDD preserves memory data but produces high leakage current, and a very low standby VDD effectively reduces leakage power but does not guarantee a reliable data-retention [8]. An optimal standby VDD is needed to maximize the leakage power saving and satisfy the data preservation requirement at the same time. This will be the main focus of our work.

To determine the optimal standby VDD of an SRAM, it is important to understand the voltage requirement for SRAM data retention. Based on an in-depth study of SRAM low voltage data-retention behavior, this work defines the boundary condition of SRAM data retention voltage (DRV), and then derives both the theoretical and practical limits of DRV as functions of design and technology parameters. These DRV analysis and results provide insights to SRAM designers and facilitate the development of low power memory standby schemes. In addition to the analytical DRV study, developed a design technique that aggressively reduces the SRAM standby leakage.

In a typical 6T - SRAM design, the bit line voltages are connected to VDD during standby mode. This cell can be represented by a flip-flop comprised of two inverters. These inverters include access transistors M5 and M6. When VDD is reduced to DRV during standby operation, all six transistors in the SRAM cell are in the sub-threshold region. Thus, the capability of SRAM data retention strongly depends on the sub-threshold current conduction behavior.

As the minimum VDD required for data preservation, DRV of an SRAM cell is a measure of its state-retention capability under very low voltage. In order to reliably preserve data in an SRAM cell, the cross-coupled inverters must have a loop gain greater than one. The stability of an SRAM cell is also

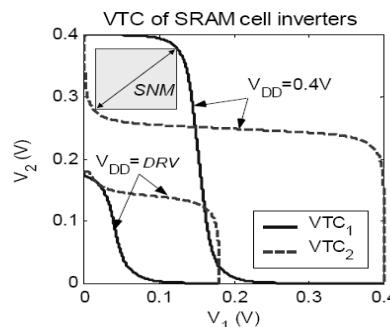

indicated by the static-noise margin (SNM) [14] [17]. As shown in Fig 2, the SNM can be graphically represented as the largest square between the voltages transfers characteristic (VTC) curves of the internal inverters.

Figure 2. VTC of SRAM Cell Inverters

Noise margin can be defined using the input voltage to output voltage transfer characteristic (VTC). In general, Noise Margin (NM) is the maximum spurious signal that can be accepted by the device when used in a system while still maintaining the correct operation. If the consequences of the noise applied to a circuit node are not latched, such noise will not affect the correct operation of the system and can thus be deemed tolerable. It is assumed that noise is presented long enough for the circuit to react, i.e. the noise is "static" or dc. A Static Noise Margin is implied if the noise is a dc source. In case when a long noise pulse is applied, the situation is quasi-static and the noise margin asymptotically approaches the SNM.

When  $V_{DD}$  scales down to DRV [19], the VTC of the cross-coupled inverters degrade to such a level that the loop gain reduces to one and SNM of the SRAM cell falls to zero. If  $V_{DD}$  is reduced below the DRV, the inverter loop switches to the other biased state determined by the deteriorated inverter VTC curves, and loses the capability to hold the stored data.

Since DRV is a function of the SRAM circuit parameters, a design optimization used to reduce DRV. At a fixed SNM, a lower DRV reduces the minimum standby  $V_{DD}$  and the leakage power. When the  $V_{DD}$  is fixed, a lower DRV improves the SNM and enhances the reliability of SRAM data retention. Traditionally, a standard SRAM cell is designed based on a performance-driven design methodology, which does not optimize the data retention reliability. For example, using a large NMOS pull-down device and a small PMOS pull-up device reduce data access delay, but cause a degraded SNM at low voltage. In order to gain a larger SNM and lower the DRV, the P/N strength ratio needs to be improved during the standby operation.

The global variation in  $V_t$  or  $L$  has a much weaker impact on DRV. This is because a global variation affects both inverters in the same direction and does not cause significant SNM degradation. The leakage current increases substantially with a high  $V_{DD}$ . This is caused by the DIBL (Drain Induced Barrier Lowering) effect in short channel transistors. In the DRV analysis of a typical SRAM cell, the DIBL effect can be ignored because all the SRAM transistors operate in a weak-inversion mode. But when  $V_{DD}$  is significantly higher than the DRV, the DIBL effect causes a rapid increase in leakage current. This phenomenon reflects the importance of low-voltage standby leakage control in CMOS technologies, where the short-channel effect increases.

The memory structure method is adopted to minimize the power consumption. The memory squaring technique is one of the structural method but in this, larger the number of words in a row the larger the power consumption. For this reason, as long as area is not an issue, memory squaring is not an optimal solution. A divided word line structure is a better solution. In this, the number of cells on the WL (Word Line) is the number of bits per word, so the length of the WL will vary because of this, structure cannot be expanded into large memories. The used structural method is partitioned structure; it is a superior solution [19] to the hierarchical word line structure. The partitions can be seen as independent parts that may be placed where required without the bounds given by the hierarchical word line structure.

The partitioning is implemented on 64 Kb SRAM architecture, which is an asynchronous design. The entire SRAM can be divided into four blocks. Each block is of 32x32 columns, where each word is 16

bits. The sense amplifier is placed with each column and column circuitry is placed below sense amplifier. The typical specification of the RAM is an access time of 10ns; therefore the sense amplifier is placed before column circuitry.

#### IV. RESULTS AND DISCUSSIONS

##### Core Cell SNM

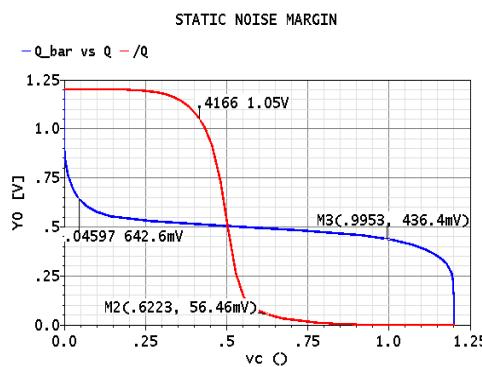

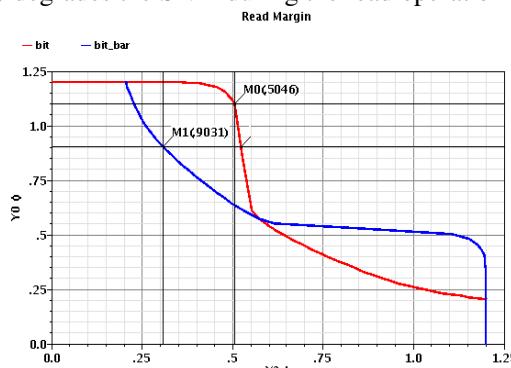

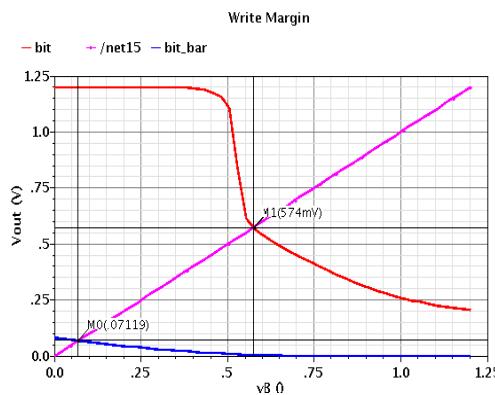

The Static Noise Margin (SNM) serves as a figure of merit in stability evaluation of SRAM cells. The Fig 3 shows the simulated result of SNM for the designed SRAM. Fig 4 and 5 represents the Read and Write margin [15] simulation results respectively. After the layout and schematic designs, the DRC and LVS procedures are verified for the designs.

Figure 3. Static noise margin

The Fig 3 plots the voltage transfer characteristic (VTC) of Inverter 2 of Fig 1 and the inverse VTC of Inverter 1. The resulting two-lobed curve is called a “butterfly curve” and is used to determine the SNM. The internal node of the bit cell that represents a zero gets pulled upward through the access transistor due to the voltage dividing effect across the access transistor and drive transistor. This increase in voltage severely degrades the SNM during the read operation (read SNM).

Figure 4: Read margin

Figure 5: Write margin

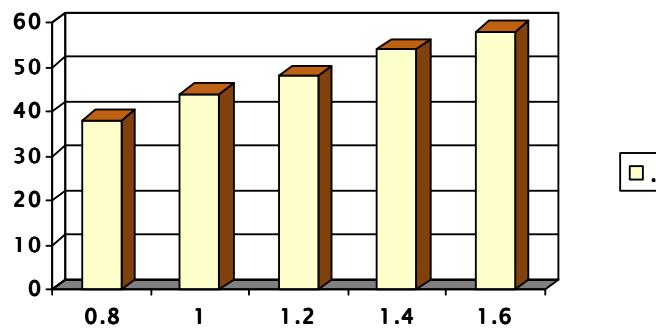

TABLE I :CR vs. SNM

| Technology(nm) | CR  | SNM(mV) |

|----------------|-----|---------|

| 130nm          | 0.8 | 38      |

|                | 1.0 | 44      |

|                | 1.2 | 48      |

|                | 1.4 | 54      |

|                | 1.6 | 58      |

The SRAM cell ratio (CR) (i.e. the ratio of the driver transistor's W/L to the access transistor's W/L) was introduced to simplify consideration of SNM optimization. The Table I show the variation of SNM with CR. From the graph of Fig 7 cell ratio vs. static noise margin, the value of static noise margin increases with the increase of cell ratio of the

SRAM cell in 130 nm technology. As the cell ratio is increased, average value of SNM increases because the driver transistor now has higher drive strength and is less susceptible to noise. At the same time, the variation in SNM reduces with increasing cell ratio. This is expected because in a wider driver transistor, there will be higher number of dopants and small variation in the number/location of these dopants will result in a smaller effect on overall device characteristics.

Figure 7. SNM vs. CR (130 nm)

## V. CONCLUSION

This paper proposes a method to investigate optimal  $V_{DD}$  with the help of SNM and also size of the cell (CR). It also addresses the critical issues in designing a low power static RAM in Deep sub

micron (DSM) 130nm technologies. The bit cell operates properly for static noise margin of 0.466V, Read margin of 0.3985V and Write margin of 0.5028V. The feature work can be extended for minimizing leakage at architecture level and also on reconfigurable cell.

## REFERENCES

- [1] K. Zhang, U. Bhattacharya, Z. Chen, F. Hamzaoglu, D. Murray, N. Vallepali, Y. Wang, B. Zheng, and M. Bohr. A 3-GHz 70-Mb SRAM in 65-nm CMOS technology with integrated column-based dynamic power supply. *IEEE Journal of Solid State Circuits (JSSC)*, 41:146–151, January 2006.

- [2] A. Bhavnagarwala, X. Tang, and J. Meindl. The impact of intrinsic device fluctuations on CMOS SRAM cell stability. *IEEE Journal of Solid-State Circuits (JSSC)*, 36:658–665, April 2001.

- [3] F. Lai and C. Lee. On-chip voltage down converter to improve SRAM read-write margin and static power for sub-nano CMOS technology. *IEEE Journal of Solid-State Circuits (JSSC)*, Vol 42, Issue -9, :2061–2070, Aug 2007.

- [4] M. Horiguchi, T. Sakata, and K. Itoh, "Switched-source-impedance CMOS circuit for low standby subthreshold current giga-scale LSI's," *IEEE Journal of Solid-State Circuits*, vol. 28, issue 11, pp. 1131–1135, Nov. 1993.

- [5] B. H. Calhoun, A. Chandrakasan, "A 256kb sub-threshold SRAM in 65nm CMOS," *IEEE International Solid-State Circuits Conference*, pp. 628, Feb 2005.

- [6] Andrew Carlson,Zheng Guo,Sriram Balasubramanian,Radu Zlatanovici,Tsu-Jae King Liu, and Borivoje Ni•Z. Guo, S. Balasubramanian, R. Zlatanovici, T. King Liu, and B. Nikolic, "FinFET-based SRAM design," in Proc. ISLPED '05, Piscataway, NJ: IEEE, 2005, pp. 2-7

- [7] H. Mizuno and T. Nagano, "Driving source-line (DSL) cell architecture for sub-1-V High-speed low power applications," *Digest of Technical Papers. Symposium on VLSI Circuits*, pp. 25–26, June 1995.

- [8] H. Kawaguchi, Y. Iataka, and T. Sakurai, "Dynamic Leakage Cut-off Scheme for Low-Voltage SRAM's," *Digest of Technical Papers, Symposium on VLSI Circuits*, pp.140-141, June 1998.

- [9] F. Li, D. Chen, L. He, and J. Cong, "Architectureevaluation for power-efficient FPGAs," In Proceedings of ACM International Symposium on Field Programmable Gate Arrays, 2003, 175—184.Feb 2002.

- [10] L. Shang, A. S. Kaviani, and K. Bathala, "Dynamic power consumption in Virtex-II FPGA family," in FPGA '02 Proceedings of the 2002 ACM/SIGDA tenth international symposium on Field-programmable gate arrays – pp 157-164.

- [11] Avant Star-Hspice Manual Volume III- MOSFET Models 1999-2000

A. Keshavarzi, S. Ma, S. Narendra, B. Bloechel, K. Mistry, T. Ghani, S. Borkar, and V. De, "Effectiveness of Reverse Body Bias for Leakage Control in Scaled Dual Vt CMOS ICs," Proceedings of the International Symposium on Low Power Electronics and Design (ISLPED), Huntington Beach, CA, August 2001, pp. 207–212.

- [12] K. Flautner et al, "Drowsy caches: simple techniques for reducing leakage power," *International Symposium on Computer Architecture*, pp. 148-157, May 2002.

- [13] J. Lohstroh, E. Seevinck, and J.D. Groot, "Worst-Case Static Noise Margin Criteria for Logic Circuits and Their Mathematical Equivalence," *IEEE Journal of Solid-State Circuits*, vol. SC-18, no. 6, pp.803-807, Dec 1983.

- [14] K. Takeda, H. Ikeda, Y. Hagihara, M. Nomura and H. Kobatake, "Redefinition of write margin for next-generation SRAM and write-margin monitoring circuit", *International Solid-State Circuits Conference Vol. 42*, No. 1, pp. 161--169, 2007.

- [15] A. Kumar, et al., "Fundamental bounds on power reduction during SRAM standby data-retention", in press, *IEEE International Symposium on Circuits and Systems*, 2007.

- [16] Seevinck E, List FJ, Lohstroh J. Static-noise margin analysis of MOS SRAM cells. *IEEE J Solid State Circuits* 1987;22:748–54.

- [17] H. Qin, R. Vattikonda, T. Trinh, Y. Cao and J. Rabaey, "SRAM cell optimization for ultra-low power standby," *Journal of Low Power Electronics*, 2(3), pp. 401–411, Dec. 2006.

- [18] Amrutur, Bharadwaj S., Design and Analysis of Fast Low Power SRAMs, dissertation at Stanford University, 1999.

## Author

**Sanjay Kr Singh**, a PhD scholar at the UK. Technical university, Dehradun, (Uttarakhand) India . He is an Asso. Professor in the Department of Electronics and Communication Engineering in Indraprastha Engineering College, Ghaziabad (Uttar Pradesh) India. He has received his M.Tech. in Electronics &Communication and B.E in Electronics and Telecommunication Engineering in the year of 2005 and 1999 respectively. His main research interests are in Deep-Sub Micron Memory Design for low power.

**Sampath Kumar V.** a PhD scholar at the UPTU Lucknow ,(Uttar Pradesh) India . He is an Assoc. Professor in the Department of Electronics and Communication Engineering in J.S.S. Academy of Technical Education, Noida, INDIA. He has received his M.Tech. in VLSI Design And B.E in Electronics and Communication Engineering in the year of 2007 and 1998 respectively. His main research interest is in reconfigurable memory design for low power.

**Arti Noor**, completed her Ph. D from Deptt. of Electronics Engg., IT BHU, Varanasi in 1990. She has started her career as Scientist-B in IC Design Group, CEERI, Pilani from 1990-95 and subsequently served there as Scientist-C from 1995-2000. In 2001 joined Speech Technology Group, CEERI Center Delhi and served there as Scientist-EI upto April 2005. In May 2005 Joined CDAC Noida and presently working as Scientist-E and HOD in M. Tech (VLSI) Division. Supervised more than 50 postgraduate theses in the area of VLSI Design, she has examined more than 50 M. Tech theses and supervising three Ph. D students in the area of Microelectronics. Her main research interest is in VLSI Design of semi or full-custom chips for implementation of specific architecture, Low power VLSI Design, Digital design.

**D S Chauhan** . He did his B.Sc Engg.(1972) in electrical engineering at I.T. B.H.U., M.E. (1978) at R.E.C. Tiruchirapalli ( Madras University ) and PH.D. (1986) at IIT/Delhi. He did his post doctoral work at Goddard space Flight Centre, Greenbelt Maryland . USA (1988-91).He has been director KNIT sultanpur in 1999-2000 and founder vice Chancellor of U.P.Tech. University (2000-2003-2006). Later on, he has served as Vice-Chancellor of Lovely Profession University (2006-07) and Jaypee University of Information Technology (2007-2009). Currently he has been serving as Vice-Chancellor of Uttarakhand Technical University for (2009-12) Tenure.

**B. K. Kaushik** ,He did his B.E. degree in Electronics and communication Engineering from C R State college of Engineering, Mурthal, Haryana in 1994.His M tech in Engineering system from Dayal bag, Agra in 1997.His obtain PhD AICTE-QIP scheme from IIT Roorkee ,India.. He has published more than 70 papers in nation and international journal and conferences. His research interest are in electronics simulation and low power VLSI designee .He is serving as a Assistant Professor in department of electronics and computer engineering, Indian institute of Technology, Roorkee, India.