# ANALYSIS OF 31 LEVEL CASCADE INVERTER USING MATLAB

G. Mahalakshmi and P. Jeyalakshmi Department of Electrical &Electronics Engineering, Sri Ramakrishna Institute of Technology, Coimbatore, India

#### ABSTRACT

This paper presents the concept of multilevel voltage source inverter and proposed a topology for 31 level cascaded multilevel inverter. In the proposed topology harmonic distortion is reduced and output voltage is nearly sinusoidal with improvement in magnitude. The simulations were done using MATLAB/Simulink software. The main objective of this paper is to compare the performance of 31 level inverter with three, five and nine level inverters. The proposed thirty- one level inverter contains the same number of switching devices as that of the standard nine level cascaded multilevel inverter. Simulations were done for three, five and nine level inverters and the THD was compared with the proposed 31 level topology. It was found that as the level of inverter increases the harmonic distortion reduced and also the output voltage of the inverter was increased with less number of switches.

KEYWORDS: Cascaded multilevel inverter, FFT Analysis, THD

#### I. Introduction

Multilevel Inverter concept was introduced in the year 1975 [1]. The term multilevel was began with three level inverter [2]. Multi level inverter has drawn tremendous interest in high power applications due to their high power capability associated with lower output harmonics and lower communication losses. [3] Many multilevel converter topologies and different methods of control have been developed in the recent literature [4]-[7]. A multilevel inverter can reduce the device voltage and output harmonics by increasing the levels. Because of this reason multilevel inverter can provide high power required for large electrical drives. The output of ideal inverter should be sinusoidal. But the wave forms of practical inverters are non-sinusoidal and contain certain harmonics. For low and medium power applications, square wave or quasi wave is acceptable.

For high power applications, low distorted sinusoidal wave forms are required. With the availability of high speed power semiconductor devices the harmonic content of output voltage can be minimized or reduced by switching techniques. The inverter can be used in hybrid electric vehicle and electric vehicle. To obtain a quality output voltage or current waveform, multilevel inverters are required. Several multilevel inverter topologies have been developed like flying capacitor, neutral point clamped and cascaded H Bridge [2]-[4]. Among these topologies cascaded H Bridge is used in this paper as it needs only less number of switches with reduced operating frequency.

A cascaded H-bridges multilevel inverter is simply a series connection of multiple H-bridge inverters. Each H-bridge inverter has the same configuration as a typical single-phase full-bridge inverter. The cascaded H-bridges multilevel inverter introduces the idea of using Separate DC Sources (SDCSs) to produce an AC voltage waveform. Each H-bridge inverter is connected to its own DC source *Vdc*. By cascading the AC outputs of each H-bridge inverter, an AC voltage waveform is produced. The model is implemented using MATLAB/Simulink software with the SimPower System Block Set. Compared to other types of multi-level inverters, the proposed thirty one level inverter having less number of switching devices. As the level increases, the number of switches get increases. But in this inverter,

the number of switches in the 31 level inverter is equal to the number of switches in the nine level inverter. Here the voltage gets increased and the THD get reduced as we go for thirty-one level. This paper presents the concept of cascade multilevel voltage source inverter and proposed a topology for 31 level inverter. This paper is organised as follows. Section II shows the concept of multilevel inverters and their advantages. Types of multilevel inverters and the three, five, nine, thirty one level topologies were presented in Section III .Section IV shows the MATLAB simulation models for all the inverter circuits and the results. Finally conclusion and future works are presented in Section V and Section VI respectively.

#### II. MULTILEVEL INVERTER

Multilevel Inverter has emerged recently as a very important alternative in the areas of high power medium voltage energy control [3]. The goal of the inverter is to produce an AC waveform from a dc supply. The dc supply usually consists of several batteries connected in series. In typical applications the input voltage for the inverters same as the dc supply voltage. Also, power is the product of voltage and current; larger applications require more power from the dc supply thus posing a design barrier. The power may be maintained by increasing the voltage and decreasing the current by the same proportion, or decreasing the voltage and increasing the current by the same proportion. If the dc supply voltage is increased (adding more batteries in series to maintain or decrease the current) for the larger power requirement, the components must be able to withstand the maximum dc supply voltage. A high supply voltage results in slower switching frequency because of the semiconductor's characteristics. If the designer chooses to deal with a larger current, then heat dissipation, and switching dv/dt become a problem, in addition to EMI problems. However, by using multiple switching levels, the components are exposed to a smaller voltage to produce the desired output waveform. The recent advancement in power electronics has initiated to improve the level of inverter instead increasing the size of filter. The total harmonic distortion of the classical inverter is very high. The performance of the multilevel inverter is better than classical inverter. The multi-level inverter was introduced as a solution to increase the converter operating voltage above the voltage limits of classical semiconductors. The output voltage wave form of a multilevel inverter is composed of the number of levels of voltages, typically obtained from capacitor voltage source [11]. The so-called multilevel starts from three levels. As the number of level reach infinity the output THD (total harmonic distortion) approaches zero. The number of achievable voltage levels, however is limited by voltage unbalance problems, voltage clamping requirement, circuit layout and packaging constraints [13]. The low voltage switches can be used in multi-level inverters. These are faster, smaller and cheaper than high voltage switches used in 2-level inverters. When switches are in series, they withstand higher voltages. Multilevel inverters offer better sinusoidal voltage waveform than 2-level inverters due to the fact that output voltage can be formed using more than two voltage levels.

# III. MULTILEVEL INVERTER CIRCUITS

The cascaded H-bridges multilevel inverter is a relatively new inverter structure. It is proposed here to solve all the problems of the multilevel inverters as well as conventional multi pulse (or PWM) inverters. This new multilevel inverter eliminates the excessively large number of *i*) bulky transformers required by conventional multi pulse inverters, *ii*) clamping diodes required by multilevel diode clamped inverters, and *iii*) flying capacitors required by multilevel flying capacitor inverters. A cascaded H-bridges multilevel inverter is simply a series connection of multiple H-bridge inverters. Each H-bridge inverter has the same configuration as a typical single-phase full-bridge inverter. The cascaded H-bridges multilevel inverter introduces the idea of using Separate DC Sources (SDCSs) to produce an AC voltage waveform. Each H-bridge inverter is connected to its own DC source *Vdc*. By cascading the AC outputs of each H-bridge inverter, an AC voltage waveform is produced.

# 3.1. Two level and Three level Inverter

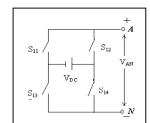

The inverter circuit used for producing two level and three level is shown in Figure. 1 Switching pattern for the inverter is given in Table 1. The number of switches used for two level and three level inverter is same.

Figure.1 Two and Three level Inverter circuit

The switching pattern to obtain the two level and three level is given in Table I.The sequence in which the switch gets ON for producing two level i.e. +Vdc and - Vdc and three level i.e.0,+Vdc,-Vdc is given .By using the appropriate switches the inverter produces the corresponding voltages.

Table 1. Switching states for two and three level inverter

| Output    | Switching States |    |     |     |  |

|-----------|------------------|----|-----|-----|--|

| voltage   | S1               | S1 | S13 | S14 |  |

| $V_{AN}$  | 1                | 2  |     |     |  |

| $V_{DC}$  | 0                | 1  | 1   | 0   |  |

| 0         | 0                | 1  | 0   | 1   |  |

|           | 0                | 1  | 0   | 1   |  |

| $-V_{DC}$ | 1                | 0  | 0   | 1   |  |

#### 3.2. Five level Inverter

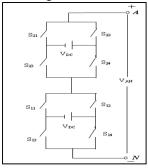

The inverter circuit used for producing five level output voltage is shown in Figure.2 the number of switches used in five level inverter circuit is eight.

Figure.2 Five level Inverter Circuit

The Switching pattern for five level inverter is shown in Table 2.

**Table 2.** Switching states for Five level inverter

| Output     | Switching State |                 |          |                 |          |          |          |          |

|------------|-----------------|-----------------|----------|-----------------|----------|----------|----------|----------|

| Voltage    | S <sub>11</sub> | S <sub>12</sub> | $S_{13}$ | S <sub>14</sub> | $S_{21}$ | $S_{22}$ | $S_{23}$ | $S_{24}$ |

|            |                 |                 |          |                 |          |          |          |          |

| $V_{AN}$   |                 |                 |          |                 |          |          |          |          |

| $2V_{DC}$  | 0               | 1               | 1        | 0               | 0        | 1        | 1        | 0        |

|            | 0               | 1               | 1        | 0               | 1        | 0        | 1        | 0        |

| $V_{DC}$   | 1               | 0               | 1        | 0               | 0        | 1        | 1        | 0        |

|            | 1               | 0               | 1        | 0               | 1        | 0        | 1        | 0        |

| 0          | 0               | 1               | 0        | 1               | 0        | 1        | 0        | 1        |

|            | 1               | 0               | 1        | 0               | 0        | 1        | 0        | 1        |

|            | 0               | 1               | 0        | 1               | 1        | 0        | 1        | 0        |

| $-V_{DC}$  | 1               | 0               | 0        | 1               | 1        | 0        | 1        | 0        |

|            | 0               | 1               | 0        | 1               | 1        | 0        | 0        | 1        |

| $-2V_{DC}$ | 1               | 0               | 0        | 1               | 1        | 0        | 0        | 1        |

#### 3.3. Nine level Inverter

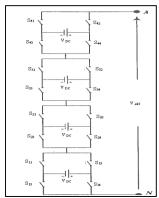

The inverter circuit used for producing nine level output voltage is shown in Figure.3.Here the number of switches used are 16.

Figure.3 Nine level Inverter Circuit

The switching pattern for producing nine level i.e. +4Vdc, +3Vdc,+2Vdc,+Vdc,0,-Vdc,-2Vdc,-3Vdc,-4Vdc is given in the Table 3 .The switches in the circuit want to get ON in the sequence given in the table to obtain the nine level. There are various combinations available for producing each level , any one of those combinations is selected for producing that level.

|                    |                 |     |     |     | <del></del> | SWILE | ining s |     |     |     | C1 111 v |     |     |     |     |     |

|--------------------|-----------------|-----|-----|-----|-------------|-------|---------|-----|-----|-----|----------|-----|-----|-----|-----|-----|

| OUTPUT<br>VOLTAGE  | SWITCHING STATE |     |     |     |             |       |         |     |     |     |          |     |     |     |     |     |

| V <sub>AN</sub>    | S11             | S12 | S13 | S14 | S21         | S22   | S23     | S24 | S31 | S32 | S33      | S34 | S41 | S42 | S43 | S44 |

| $4V_{dc}$          | 0               | 1   | 1   | 0   | 0           | 1     | 1       | 0   | 0   | 1   | 1        | 0   | 0   | 1   | 1   | 0   |

| $3V_{dc}$          | 0               | 1   | 1   | 0   | 0           | 1     | 1       | 0   | 0   | 1   | 1        | 0   | 1   | 0   | 1   | 0   |

|                    | 0               | 1   | 1   | 0   | 0           | 1     | 1       | 0   | 1   | 0   | 1        | 0   | 0   | 1   | 1   | 0   |

| 1                  | 0               | 1   | 1   | 0   | 1           | 0     | 1       | 0   | 0   | 1   | 1        | 0   | 0   | 1   | 1   | 0   |

| 1                  | 1               | 0   | 1   | 0   | 0           | 1     | 1       | 0   | 0   | 1   | 1        | 0   | 0   | 1   | 1   | 0   |

| $2V_{dc}$          | 0               | 1   | 1   | 0   | 0           | 1     | 1       | 0   | 1   | 0   | 1        | 0   | 1   | 0   | 1   | 0   |

|                    | 0               | 1   | 1   | 0   | 1           | 0     | 1       | 0   | 0   | 1   | 1        | 0   | 1   | 0   | 1   | 0   |

| 1                  | 1               | 0   | 1   | 0   | 0           | 1     | 1       | 0   | 0   | 1   | 1        | 0   | 1   | 0   | 1   | 0   |

| 1                  | 1               | 0   | 0   | 1   | 0           | 1     | 1       | 0   | 0   | 1   | 1        | 0   | 0   | - 1 | 1   | 0   |

| 1                  | 0               | 1   | 1   | 0   | 1           | 0     | 0       | 1   | 0   | 1   | 1        | 0   | 0   | 1   | 1   | 0   |

|                    | 1               | 0   | 0   | 1   | 0           | 1     | 1       | 0   | 0   | 1   | 1        | 0   | 0   | 1   | 1   | 0   |

| $V_{dc}$           | 0               | 1   | 1   | 0   | 1           | 0     | 1       | 0   | 1   | 0   | 1        | 0   | 1   | 0   | 1   | 0   |

| 1                  | 1               | 0   | 1   | 0   | 1           | 0     | 1       | 0   | 1   | 0   | 1        | 0   | 0   | 1   | 1   | 0   |

| 1                  | 1               | 0   | 1   | 0   | 0           | 1     | 1       | 0   | 1   | 0   | 1        | 0   | 1   | 0   | 1   | 0   |

| 1                  | 1               | 0   | 1   | 0   | 1           | 0     | 1       | 0   | 0   | 1   | 1        | 0   | 1   | 0   | 1   | 0   |

| 1                  | 1               | 0   | 0   | 1   | 0           | 1     | 1       | 0   | 1   | 0   | 1        | 0   | 0   | 1   | 1   | 0   |

|                    | 1               | 0   | 1   | 0   | 0           | 1     | 1       | 0   | 1   | 0   | 0        | 1   | 0   | - 1 | 1   | 0   |

| 0                  | 1               | 0   | 1   | 0   | 1           | 0     | 1       | 0   | 1   | 0   | 1        | 0   | 1   | 0   | 1   | 0   |

|                    | 0               | - 1 | 0   | 1   | 0           | 1     | 0       | 1   | 0   | 1   | 0        | 1   | 0   | 1   | 0   | 1   |

|                    | 1               | 0   | 0   | 1   | 0           | 1     | 1       | 0   | 1   | 0   | 0        | 1   | 0   | - 1 | 1   | 0   |

| 1                  | 1               | 0   | 0   | 1   | 0           | 1     | 1       | 0   | 0   | 1   | 1        | 0   | 1   | 0   | 0   | 1   |

|                    | 1               | 0   | 1   | 0   | 1           | 0     | 1       | 0   | 1   | 0   | 0        | 1   | 0   | 1   | 1   | 0   |

|                    | 1               | 0   | 1   | 0   | 0           | 1     | 1       | 0   | 1   | 0   | 0        | 1   | 1   | 0   | 1   | 0   |

| - V <sub>de</sub>  | 1               | 0   | 1   | 0   | 0           | 1     | 1       | 0   | 1   | 0   | 0        | 1   | 1   | 0   | 0   | 1   |

|                    | 1               | 0   | 0   | 1   | 1           | 0     | 1       | 0   | 1   | 0   | 1        | 0   | 1   | 0   | 1   | 0   |

|                    | 1               | 0   | 1   | 0   | 1           | 0     | 1       | 0   | 1   | 0   | 1        | 0   | 1   | 0   | 0   | 1   |

|                    | 0               | 1   | 1   | 0   | 1           | 0     | 0       | 1   | 1   | 0   | 0        | 1   | 1   | 0   | 1   | 0   |

|                    | 0               | 1   | 1   | 0   | 1           | 0     | 1       | 0   | 1   | 0   | 0        | 1   | 1   | 0   | 0   | 1   |

| -2V <sub>dc</sub>  | 1               | 0   | 1   | 0   | 1           | 0     | 0       | 1   | 1   | 0   | 0        | 1   | 1   | 0   | 1   | 0   |

| 1                  | <u> </u>        | 0   | 0   | 1   | 1           | 0     | 1       | 0   | 1   | 0   | 1        | 0   | 1   | 0   | 0   | 1   |

| l                  | 1               | 0   | 0   | 1   | 0           | 1     | 1       | 0   | 1   | 0   | 0        | 1   | 1   | 0   | 0   | 1   |

| l                  | 1               | 0   | 0   | 1   | 1           | 0     | 1       | 0   | 1   | 0   | 0        | 1   | 1   | 0   | 1   | 0   |

| 2.1/               | 1               | 0   | 1   | 0   | 1           | 0     | 0       | 1   | 1   | 0   | 0        | 1   | 1   | 0   | 1   | 0   |

| -3 V <sub>de</sub> | 1               | 0   | 1   | 0   | 1           | 0     | 0       | 1   | 1   | 0   | 0        | 1   | 1   | 0   | 0   | 1   |

| l                  | 1               | 0   | 0   | 1   | 1           | 0     | 0       | 1   | 1   | 0   | 0        | 1   | 1   | 0   | 1   | 0   |

| l                  | 1               | 0   | 0   | 1   | 1           | 0     | 1       | 0   | 1   | 0   | 0        | 1   | 1   | 0   | 0   | 1   |

|                    | 1               | 0   | 0   | I   | 1           | 0     | 0       | 1   | I   | 0   | 1        | 0   | 1   | 0   | 0   | 1   |

0

0

**Table 3.** Switching states for Nine level inverter

# 3.4. Thirty one level Inverter

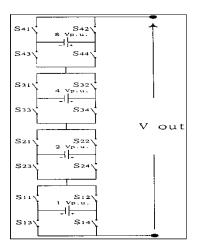

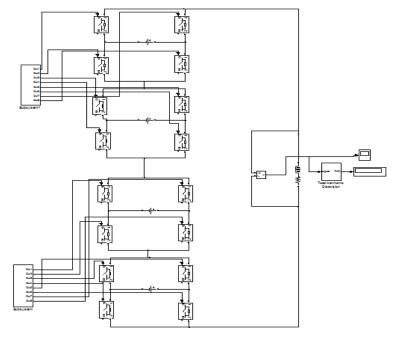

By using dc voltage sources with a magnitude ratio of 1:2:4:8, the traditional nine-level inverter can be turned into a 31-level inverter. The circuit used for nine level and thirty-one level inverter is same except the magnitude ratio of the dc voltage source. The circuit with the voltage magnitude circuit is shown in Figure.4

Figure.4 Thirty one level Inverter Circuit

This circuit topology is identical to that of a traditional nine-level inverter, except that unequal separate voltages are employed. By using the separate dc voltage sources with the ratio of 1:2:4:8 and by controlling the switching of the cascade inverter modules, 31 discrete voltage levels (from -15 Vp.u to 15 Vp.u) can be generated. The switching pattern for the proposed 31 level is given in Table 4. The number of switches used in Thirty-one level inverter is sixteen same as conventional nine level.

| Voltage    | Switching | Voltage    | Switching |

|------------|-----------|------------|-----------|

| (per unit) | patterns  | (per unit) | patterns  |

| 15         | 1+2+4+8   | -15        | -1-2-4-8  |

| 14         | 2+4+8     | -14        | -2-4-8    |

| 13         | 1+4+8     | -13        | -1-4-8    |

| 12         | 4+8       | -12        | -4-8      |

| 11         | 1+2+8     | -11        | -1-2-8    |

| 10         | 2+8       | -10        | -2-8      |

| 9          | 1+8       | -9         | -1-8      |

| 8          | 8         | -8         | -8        |

| 7          | 1+2+4     | -7         | -1-2-4    |

| 6          | 2+4       | -6         | -2-4      |

| 5          | 1+4       | -5         | -1-4      |

| 4          | 4         | -4         | -4        |

| 3          | 1+2       | -3         | -1-2      |

| 2          | 2         | -2         | -2        |

| 1          | 1         | -1         | -1        |

| 0          | 0         |            |           |

**Table 4.** Switching states for Thirty one level inverter

# IV. SIMULATION MODEL AND RESULT

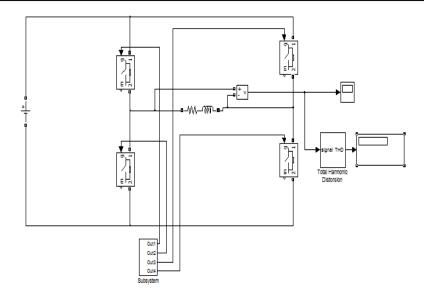

All the multilevel inverters are implemented in MATLAB SIMULINK software and the simulation results were compared. The MATLAB Simulink model of three level inverter is shown in Figure. 5. The output of the inverter is shown in Figure.6

Figure.5 Simulink model of Three level inverter

Figure.6 Output wave form of Three level inverter

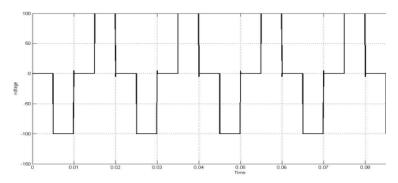

The MATLAB Simulink model of five level inverter is shown in Figure. 7. The output of the inverter is shown in Figure. 8.

Figure.7 Simulink model of Five level inverter

Figure.8 Output wave form of Five level inverter

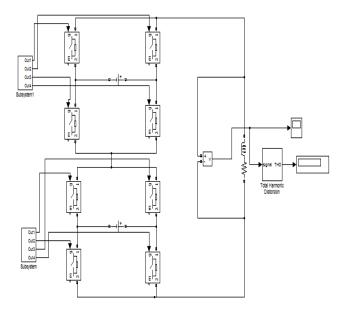

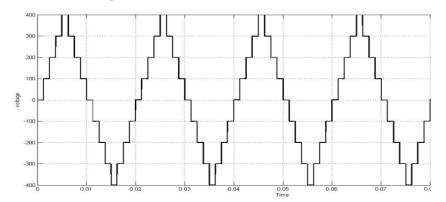

The MATLAB Simulink model of Nine level inverter is shown in Figure. 9. The output of the inverter is shown in Figure. 10

Figure.9 Simulink model of Nine level inverter

Figure.10 Output wave form of Nine level inverter

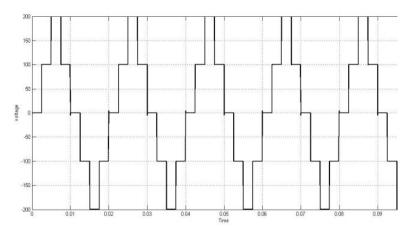

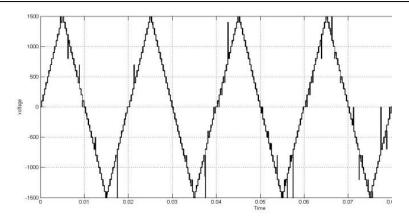

The output of the Thirty one level inverter is shown in Figure. 11

Figure.11 Output wave form of Thirty-one level inverter

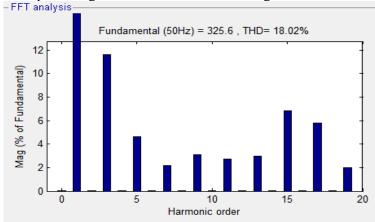

# FFT analysis

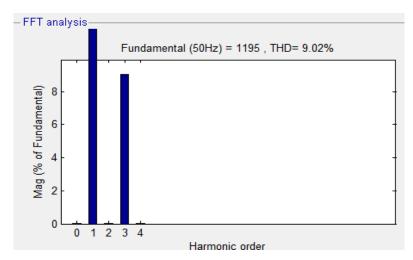

Total Harmonic Distortion of Thirty-one level inverter has 9.02% which is illustrated in Figure.13. The Thirty –one level THD values are reduced compared to the Three, Five and Nine level inverter. Also the fundamental output voltage is increased as shown in Figure.13

Figure.12 FFT analysis of Nine level inverter

Figure.13 FFT analysis of Thirty-one level inverter

The analysis result of the THD for all the levels has been simulated and tabulated in Table 5

-----

| Table 5 THD analysis result |            |        |  |  |  |  |

|-----------------------------|------------|--------|--|--|--|--|

| S.No                        | Levels     | THD    |  |  |  |  |

| 1                           | Three      | 0.4959 |  |  |  |  |

| 2                           | Five       | 0.2902 |  |  |  |  |

| 3                           | Nine       | 0.1802 |  |  |  |  |

| 4                           | Thirty-one | 0.0902 |  |  |  |  |

From the THD analysis result, it is found that as the level increases THD reduces.

# V. CONCLUSION

In this paper simulation studies was done for three level ,five level ,nine level and thirty one level cascaded multi-level inverter .Nine level inverter can be extended to thirty one level cascaded multilevel inverter by using dc voltage sources with a magnitude ration of 1:2:4:8. But it was done with the same number of switches as the nine level inverter. This results in reduced harmonics and better voltage output. When the level increases from three level to thirty one level, the total harmonic distortion get reduced. The output voltage waveform more or less resembles pure sinusoidal waveform which improves the fundamental output voltage and reduces harmonics.

# VI. FUTURE WORK

In future this work can be compared with PWM based switching and multicarrier switching methods. Since most of the applications include three phase circuits, it can be extended to three phase multilevel inverter also. This work can also be extended to the Induction motor drives and the performance can be analysed.

#### REFERENCES

- [1] R. H. Baker and L. H. Bannister, "Electric power converter," U.S. Patent 3 867 643, Feb. 1975.

- [2] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point clamped PWM inverter," *IEEE Trans. Ind. Appl.*, vol. IA-17, no. 5, pp. 518–523, Sep./Oct. 1981.

- [3] T.J. Kim, D.W. Kang, Y. H. Lee and D.S. Hyaun, "The analysis of conduction and switching losses in multi-level inverter system" in Proc. Power ElectronicsSpec.Conf., 2001, pp 1363-1368.

- [4] J.Rodrigues,B. Wu.S.Bernet. J.Pontt, and Kouro,"Multilevel voltage source converter topologies for industrial mediumvoltagedrives,"IEEETrans.Ind.Electron.,vol.54, no6,pp.2930-2945,Dec2007.

- [5] H.Abu-ub, J.Holtz, J.Rodriquez, and G.Baoming,"Medium voltage multilevel converters-Stste of the art, challenges and requirements in industrial applications," IEEE Trans. Ind. Electron, vol.57, no8, pp2251-2596, Aug2010.

- [6] E.Babaei and S.H.Hosseini,"New cascaded multilevel inverter topology with minimum number of switches", J. Energ convers. Manag., vol50, no.11, pp2761-2767, Nov. 2009

- [7] E.Babaei and M.S.Moeinian,"Asymmetric cascaded multilevel inverter with charge balance control of a low resolution symmetric subsystem,"J.Energy Convers.Manag.,vol51,no11,pp.2272-2278,Nov.2010

- [8] Murugesan.G,Jabagar sathik.M and Praveen.M,"A new multilevel Inverter Topology with less number of Switches" International journal of Engineering Science and Technology,Vol.3 No.2,Feb2011.pp1500-1510.

- [9] K.Surya Suresh and M.Vishnu Prasad,"Analysis and Simulation of New seven level inverter Topology" International Journal of Scientific and Research Publications, Volume 2, Issue 4, April 2012 ,pp 1-6.

- [10] Dhaval Patel, Himanshu N. Chaudhari, Hina Chandwani & Anand Damle." Analysis and Simulation of Asymmetrical Type Multilevel Inverter using Optimization Angle Control Technique", International Journal of Advanced Electrical and Electronics Engineering, (IJAEEE), ISSN (Print): 2278-8948, Volume-1, Issue-3, 2012.

- [11] M. R. Banaei and E. Salary," Asymmetric Cascaded Multi-level Inverter: A Solution to Obtain High Number of Voltage Levels", J Electr Eng Technol Vol. 8, No. 2: 316-325, 2013.

- [12] Jannu Ramu, S.J.V. Prakash, K. Satya Srinivasu, R.N.D. Pattabhi Ram, M. Vishnu Prasad and Md. Mazhar Hussain, "Comparison between Symmetrical and Asymmetrical Single Phase Seven Level Cascade H-Bridge Multilevel Inverter with PWM Topology" International Journal of

multidisciplinary Sciences And Engineering, Vol. 3, No. 4, April 2012

[13] Mariusz Malinowski, Senior Member, IEEE, K. Gopakumar, Senior Member, IEEE, Jose Rodriguez, Senior Member, IEEE, and Marcelo A. Pérez, Member, IEEE," A Survey on Cascaded Multilevel Inverters", IEEE Transactions On Industrial Electronics, Vol. 57, No. 7, July 2010.

#### **AUTHORS**

**G. Mahalakshmi** received B.E degree in Electrical &Electronics Engineering from Periyar University, Salem and M.E in Power Electronics & Drives from Anna University, Chennai in the year 2008.Her area of interest is Power electronics and Electrical drives. Currently she is working as Assistant Professor of EEE department in Sri Ramakrishna Institute of Technology, Coimbatore.

**P.** Jeyalakshmi received B.E degree in Electrical &Electronics Engineering from Manonmaniam Sundaranar University, Tirunelveli and M.E in Power Electronics & Drives from Anna university, Tirunelveli in the year 2010.Her area of interest is Power Electronics and drives. Currently she is working as Assistant Professor of EEE department in Sri Ramakrishna Institute of Technology, Coimbatore.